Chapter 5

Signal Timing

DIO 6533 User Manual

5-16

© National Instruments Corporation

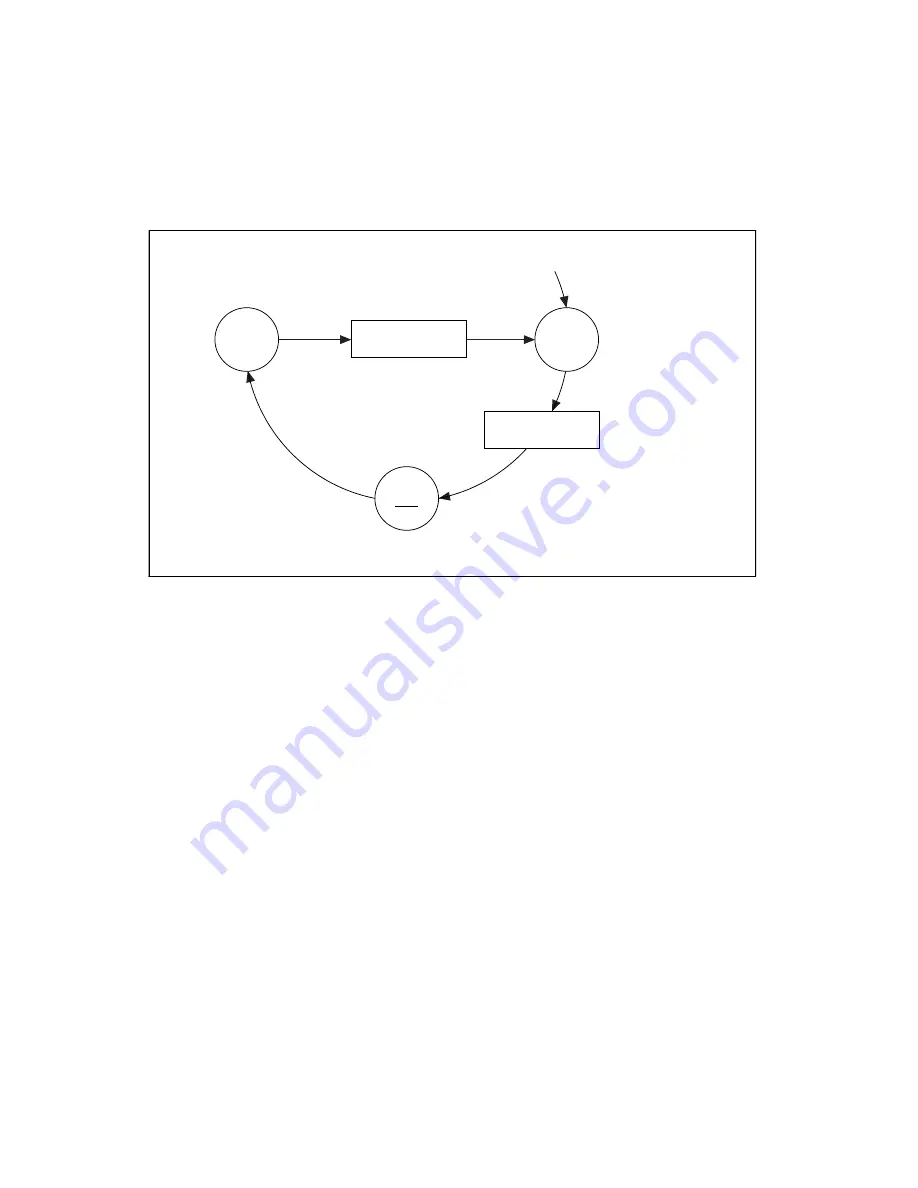

Figure 5-13 shows an output transfer in leading-edge mode.

Figure 5-13. Leading-Edge Mode Output

Leading-Edge Mode Timing Specifications

and

show the timing diagrams for leading-edge

mode.

Wait

For

Data

Wait

For

REQ

Programmable

Delay

Programmable

Delay

Wait

For

REQ

When REQ

Asserted

When 6533 Device

Has Data to Output,

Output Data*

Clear

ACK

Pulse

When REQ

Unasserted

Initial State

ACK Cleared

Send

ACK

Pulse

* With REQ-edge latching enabled, the data written is

delayed until the next inactive-going REQ edge.