Programming Model

http://www.motorola.com/computer/literature

3-65

3

Register, and further writes to the I

2

C Control Register will not

be allowed until after the I

2

C Status Register is read. A read

from the I

2

C Status Register will clear this bit.

i2_ackin

This bit is set if the addressed slave device is acknowledged to

either a start sequence or data writes from the I

2

C master

controller and cleared otherwise. The I

2

C master controller will

automatically clear this bit at the beginning of the next valid I

2

C

operation.

i2_cmplt

This bit is set after the I

2

C master controller has successfully

completed the requested I

2

C operation and cleared at the

beginning of every valid I

2

C operation. This bit is also set after

power-up.

I

2

C Transmitter Data Register

I2_DATAWR The I2_DATAWR contains the transmit byte for I

2

C data

transfers. If a value is written to I2_DATAWR when the i2_start

and i2_enbl bits in the I

2

C Control Register are set, a start

sequence is generated immediately followed by the transmission

of the contents of the I2_DATAWR to the responding slave

device. The I2_DATAWR[24:30] is the device address, and the

I2_DATAWR[31] is the WR/RD bit (0=WRite, 1=ReaD). After

a start sequence with I2_DATAWR[31]=0, subsequent writes to

the I

2

C Transmitter Data Register will cause the contents of

I2_DATAWR to be transmitted to the responding slave device.

After a start sequence with I2_DATAWR[31]=1, subsequent

writes to the I

2

C Transmitter Data Register (data=don’t care)

will cause the responding slave device to transmit data to the I

2

C

Receiver Data Register. If a value is written to I2_DATAWR

(data=don’t care) when the i2_stop and i2_enbl bits in the I

2

C

Control Register are set, a stop sequence is generated.

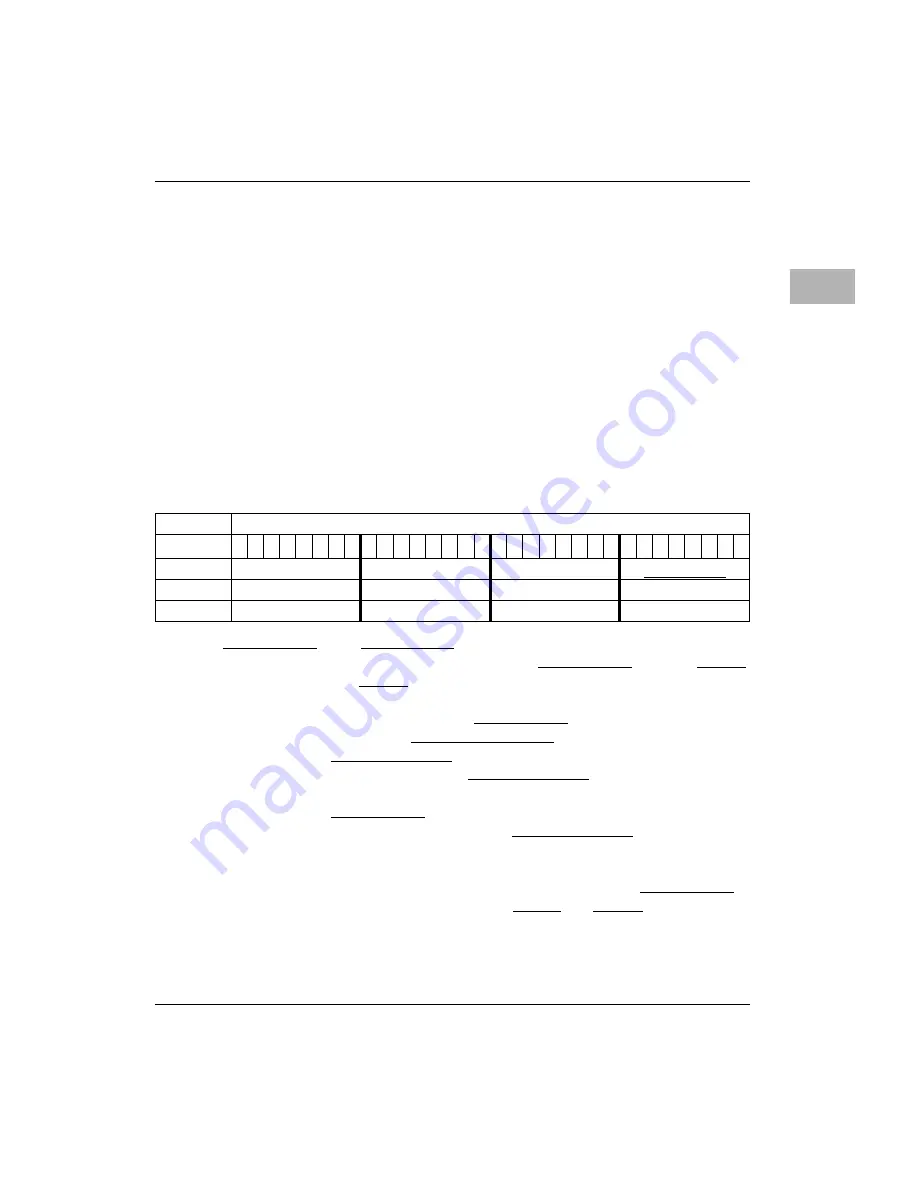

Address

$FEF800A8

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

I2_DATAWR

Operation

READ ZERO

READ ZERO

READ ZERO

READ/WRITE

Reset

X

X

X

0 PL

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...