3-58

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

rom b we

When rom b we is set, writes to Block B ROM/Flash are

enabled. When rom b we is cleared, they are disabled.

Refer back to

for more details.

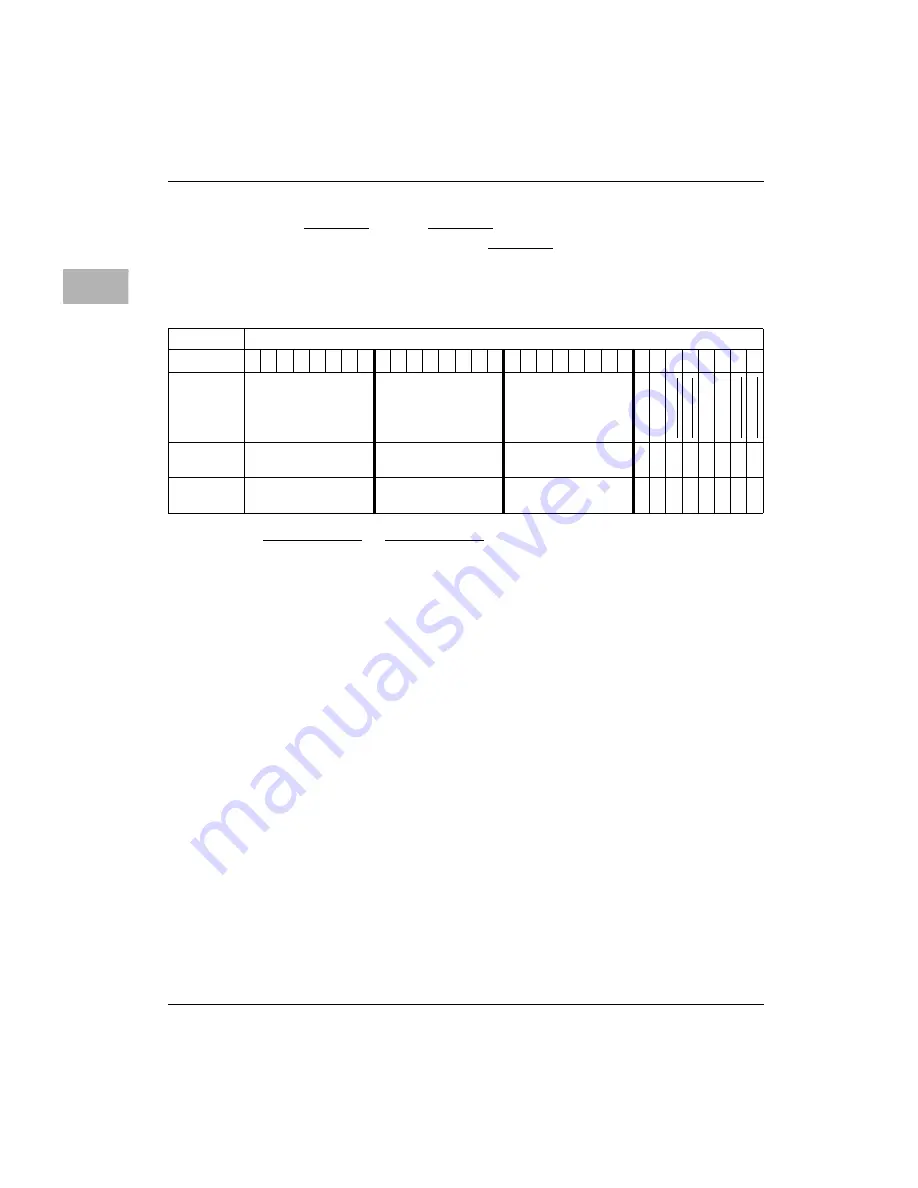

ROM Speed Attributes Registers

rom_a_spd0,1

rom_a_spd0,1 determine the access timing used for

ROM/Flash Block A. The encoding of these bits are

shown in

.

The device access times shown in the table are

conservative and allow time for buffers on address,

control, and data signals. For more accurate information

see the section entitled Timing Specifications for

ROM/Flash Signals further on in this manual, along with

the section titled ROM/Flash Read Timing Diagram.

Address

$FEF80060

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

0

0

ro

m a sp

d

0

ro

m a sp

d

1

0

0

ro

m b

sp

d

0

ro

m b

sp

d

1

Operation

READ ZERO

READ ZERO

READ ZERO

R

R

R/W

R/W

R

R

R/W

R/W

Reset

X

X

X

X

X

0 P

L

0 P

L

X

X

0 P

L

0 P

L

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...