M68360QUADS-040 Hardware User’s Manual

Hardware Preparation and Installation

13

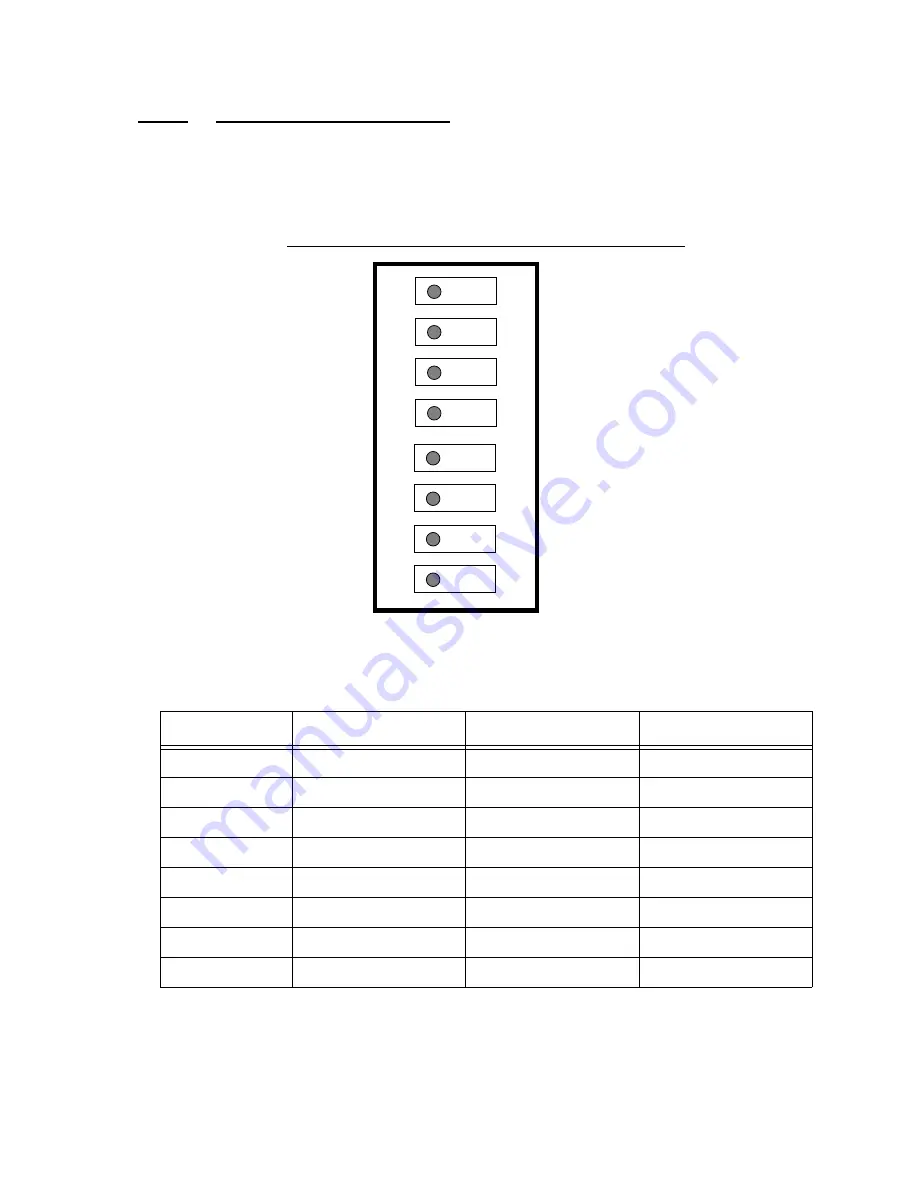

2.3.1

ADI Port Address Selection

The M68360QUADS-040 can have eight possible slave addresses set for its ADI port, enabling up to eight

M68360QUADS-040 boards to be connected to the same ADI board in the host computer. The selection

of the slave address is done by setting switches 6, 7 & 8 in the Dip-Switch. Switch 6 stands for the most-

significant bit of the address and switch 8 stands for the least-significant bit. If the switch is in the ’ON’ state,

it stands for logical ’1’. In FIGURE 2-2 DSW1 is shown to be configured to address ’0’.

FIGURE 2-2 Configuration Dip-Switch - DSW1

Table 2-1 describes the switch settings for each slave address:

Table 2-1 ADI Address Selection

ADDRESS

Switch 6

Switch 7

Switch 8

0

OFF

OFF

OFF

1

OFF

OFF

ON

2

OFF

ON

OFF

3

OFF

ON

ON

4

ON

OFF

OFF

5

ON

OFF

ON

6

ON

ON

OFF

7

ON

ON

ON

DSW1

ON

5

6

7

8

1

2

3

4

SEL2: ON - ’1’, OFF ’0’

SEL1: ON - ’1’, OFF ’0’

SEL0: ON - ’1’, OFF ’0’

OPT2: ON - ’1’, OFF ’0’

OPT1: ON - ’1’, OFF ’0’

OPT0: ON - ’1’, OFF ’0’

CDIS~: ON - DISABLED

MDIS~: ON - DISABLED

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..