16-26

MCF5272 User’s Manual

Operation

If a break condition is detected (RxD is low for the entire character including the stop bit),

a character of all zeros is loaded into the receiver holding register (RHR) and

USRn[RB,RxRDY] are set. RxD must return to a high condition for at least one-half bit

time before a search for the next start bit begins.

The receiver detects the beginning of a break in the middle of a character if the break

persists through the next character time. If the break begins in the middle of a character, the

receiver places the damaged character in the Rx FIFO stack and sets the corresponding

USRn error bits and USRn[RxRDY]. Then, if the break lasts until the next character time,

the receiver places an all-zero character into the Rx FIFO and sets USRn[RB,RxRDY].

16.5.2.3 Transmitter FIFO

Whenever the CPU writes a character for transmission into UTB, the character is placed

into the 24-byte transmitter FIFO. UTB fills the last spot in the FIFO and holds the last

character to be transmitted. Visibility into the status of the FIFO is provided by various bits

and interrupts, as shown in Table 16-16.

16.5.2.4 Receiver FIFO

The FIFO stack is used in the UART’s receiver buffer logic. The FIFO is 24 bytes deep. The

receive buffer consists of the FIFO and a receiver shift register connected to the RxD (see

Figure 16-24). Data is assembled in the receiver shift register and loaded into the top empty

receiver holding register position of the FIFO. Similar to the transmitter, several status bits

and interrupts provide visibility into the status of the FIFO.

In addition to the data byte, three status bits, parity error (PE), framing error (FE), and

received break (RB), are appended to each data character in the FIFO; OE (overrun error)

is not appended. By programming the ERR bit in the channel’s mode register (UMR1n),

status is provided in character or block modes.

USRn[RxRDY] is set when at least one character is available to be read by the CPU. A read

of the receiver buffer produces an output of data from the top of the FIFO stack. After the

read cycle, the data at the top of the FIFO stack and its associated status bits are popped and

the receiver shift register can add new data at the bottom of the stack. The FIFO-full status

bit (FFULL) is set if all 24 stack positions are filled with data. Either the RxRDY or FFULL

bit can be selected to cause an interrupt.

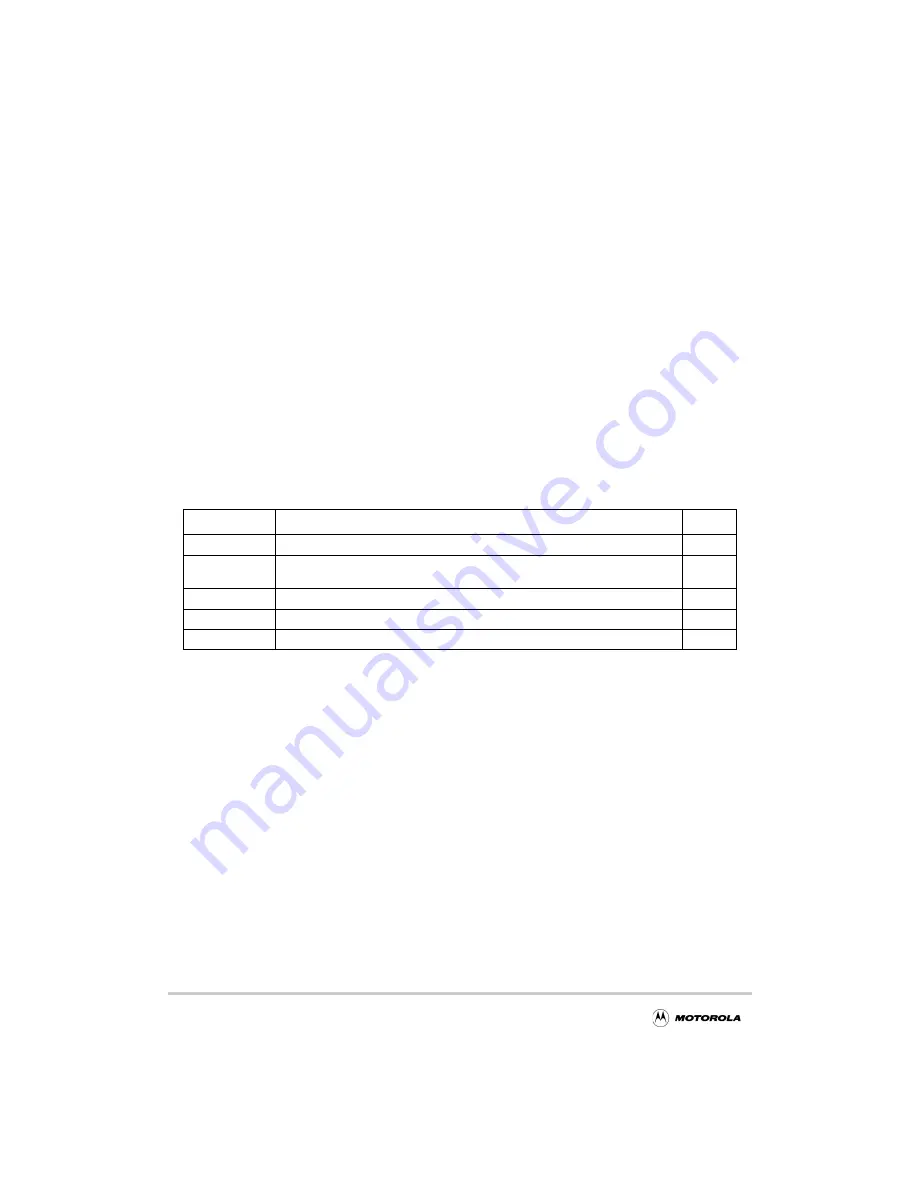

Table 16-16. Transmitter FIFO Status Bits

Status Bit

Indicated Condition

Interrupt

USR[TxEMP] = 1 The transmitter FIFO and shift register are empty and a data underrun occurred.

USR[TxRDY] = 1

At least one FIFO stage is available for a character to be transmitted. If this bit is

cleared, the FIFO is full and a subsequent write to the FIFO will be ignored.

Yes

USR[FFULL] = 1

The programmed level of emptiness (UTF[TXS]) has been reached.

Yes

UTF[TXS]

Indicates the level of emptiness of the transmitter FIFO

UTF[TXB]

Indicates the number of characters, 0–24, in the transmitter FIFO

Summary of Contents for DigitalDNA ColdFire MCF5272

Page 1: ...MCF5272UM D Rev 0 02 2001 MCF5272 ColdFire Integrated Microprocessor User s Manual ...

Page 38: ...xxxviii MCF5272 User s Manual TABLES Table Number Title Page Number ...

Page 58: ...1 10 MCF5272 User s Manual MCF5272 Specific Features ...

Page 90: ...2 42 MCF5272 User s Manual Exception Processing Overview ...

Page 96: ...3 6 MCF5272 User s Manual MAC Instruction Execution Timings ...

Page 158: ...5 46 MCF5272 User s Manual Motorola Recommended BDM Pinout ...

Page 184: ...7 12 MCF5272 User s Manual Interrupt Controller Registers ...

Page 338: ...13 44 MCF5272 User s Manual Application Examples ...

Page 414: ...18 6 MCF5272 User s Manual PWM Programming Model ...

Page 452: ...19 38 MCF5272 User s Manual Power Supply Pins ...

Page 482: ...20 30 MCF5272 User s Manual Reset Operation ...

Page 492: ...21 10 MCF5272 User s Manual Non IEEE 1149 1 Operation ...