9

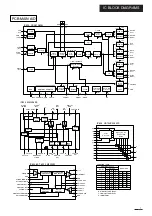

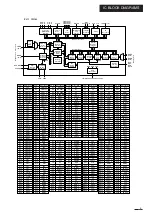

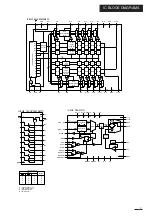

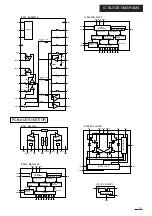

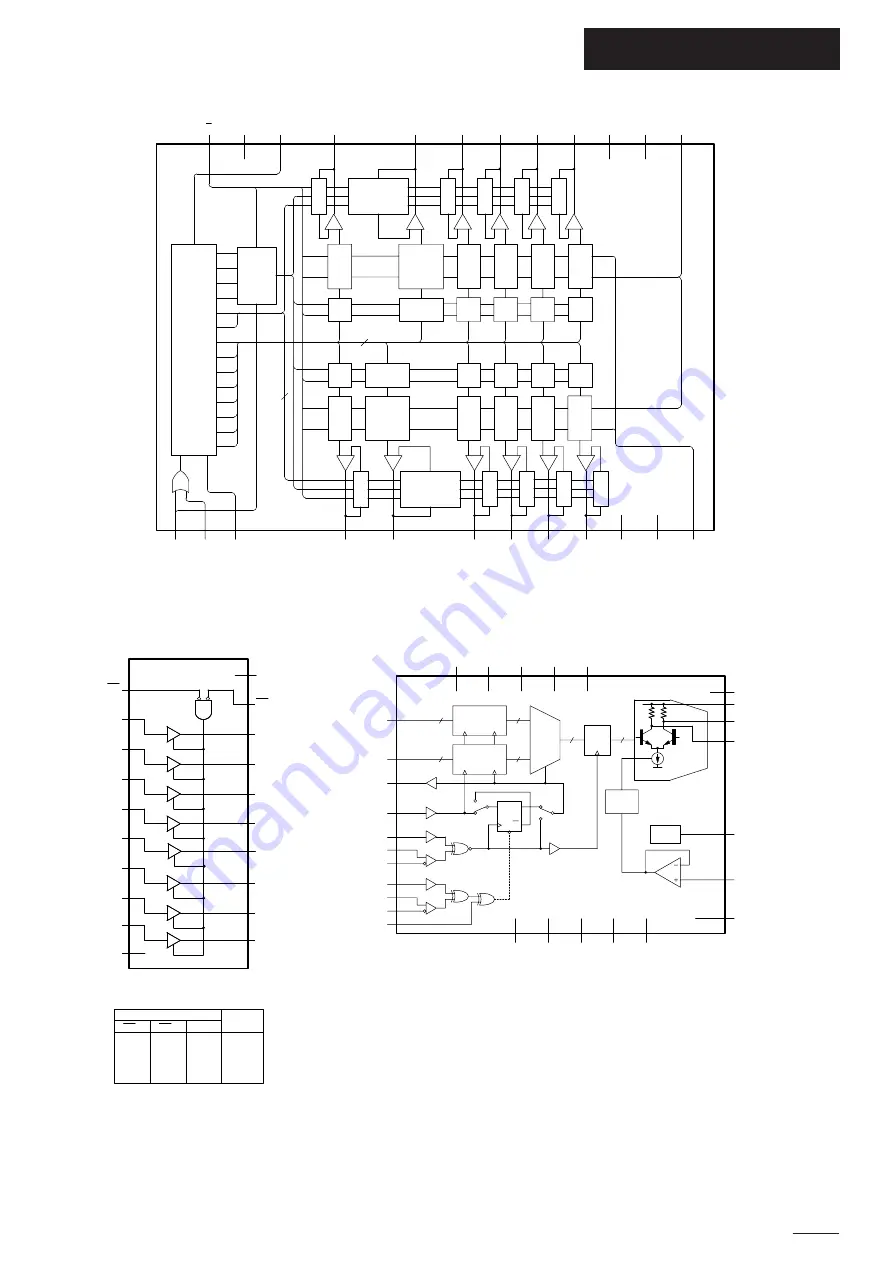

IC5M2,5M3 M62358FP

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

14 bit Shift Register

MSB

LSB

Address

Decoder

1

LD

CLK

2

D1

3

–

+

G

R-2R

–

+

Gain

Determination

Latch

8 bit

Upper

Segment

R-2R

–

+

G

R-2R

8 bit

Latch

L

L

–

+

G

R-2R

L

–

+

G

R-2R

L

–

+

G

R-2R

L

Ao6

Ao5

Ao4

Ao3

Ao2

Ao1

21

20

19

18

17

16

8 bit

Latch

L

L

L

L

L

R-2R

8 bit

Upper

Segment

R-2R

R-2R

R-2R

R-2R

R-2R

–

+

–

+

–

+

–

+

–

+

–

+

Gain

Determination

Latch

G

G

G

G

G

4

5

6

Ao7

Ao8

Ao9

7

8

9

Ao10

Ao11

Ao12

22

23

24

R

VDD

D0

10

11

12

N.C.

GND

VrefL

15

14

13

N.C.

VCC

VrefU

2

12

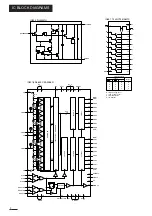

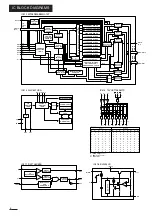

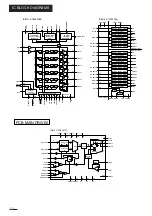

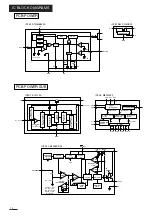

IC5M4 74VHCT541AMTC

1

2

3

4

5

6

7

8

12

13

16

17

18

OE

I0

I1

I2

I3

I4

I5

I6

O6

O5

O4

O3

O2

O1

O0

9

I7

19

11

O7

15

14

10

GND

Vcc

20

DC2

Output

TRUTH TABLE

H

Z

Z

L

L

X

H

L

H

L

X

X

L

L

H

X

I

Inputs

OE1

OE2

H = High Voltage Level

L = Low Voltage Level

Z = Higt Impedance

X = Immaterial

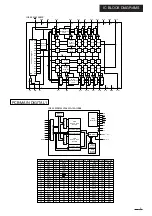

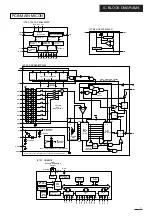

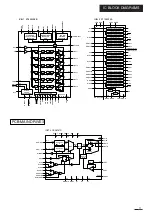

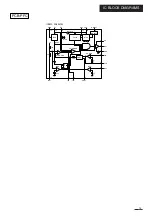

IC8G0 CXA3197R

Input Latch

A

Input Latch

B

MUX

10bit

10bit

10bit

Latch

10bit

10bit

10bit

AGND2

RO = 50

Ω

D Q

Q

Current

Cont.

RGB

30

32

31

36

6 ~ 1

48 ~ 45

16 ~ 7

18

17

19

20

21

22

23

24

39

44

25

26

27

28

42

29

38

40

41

35

33,37

34

DVcc1

DVcc2 VOCLP

INV

PS

DGND1 DGND2

C1

C2

C3

DIV2OUT

DA0 ~ DA9

DB0 ~ DB9

DIV2IN

CLK/T

CLKP/E

CLKN/E

RESET/T

RESETP/E

RESETN/E

R POLARITY

AVcc2

AVccO

AOUTP

AOUTN

VREF

VSET

AGND2

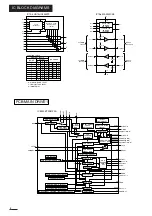

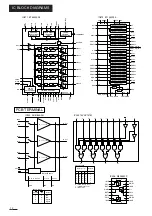

IC BLOCK DIAGRAMS

Summary of Contents for S290U

Page 83: ...16 ...

Page 180: ...113 SYMBOL NO ADDRESS X7A1 A 3 PCB MAIN COMPONENT SIDE ...

Page 188: ...121 ...