Serial Peripheral Interface Controller

UG0331 User Guide Revision 15.0

535

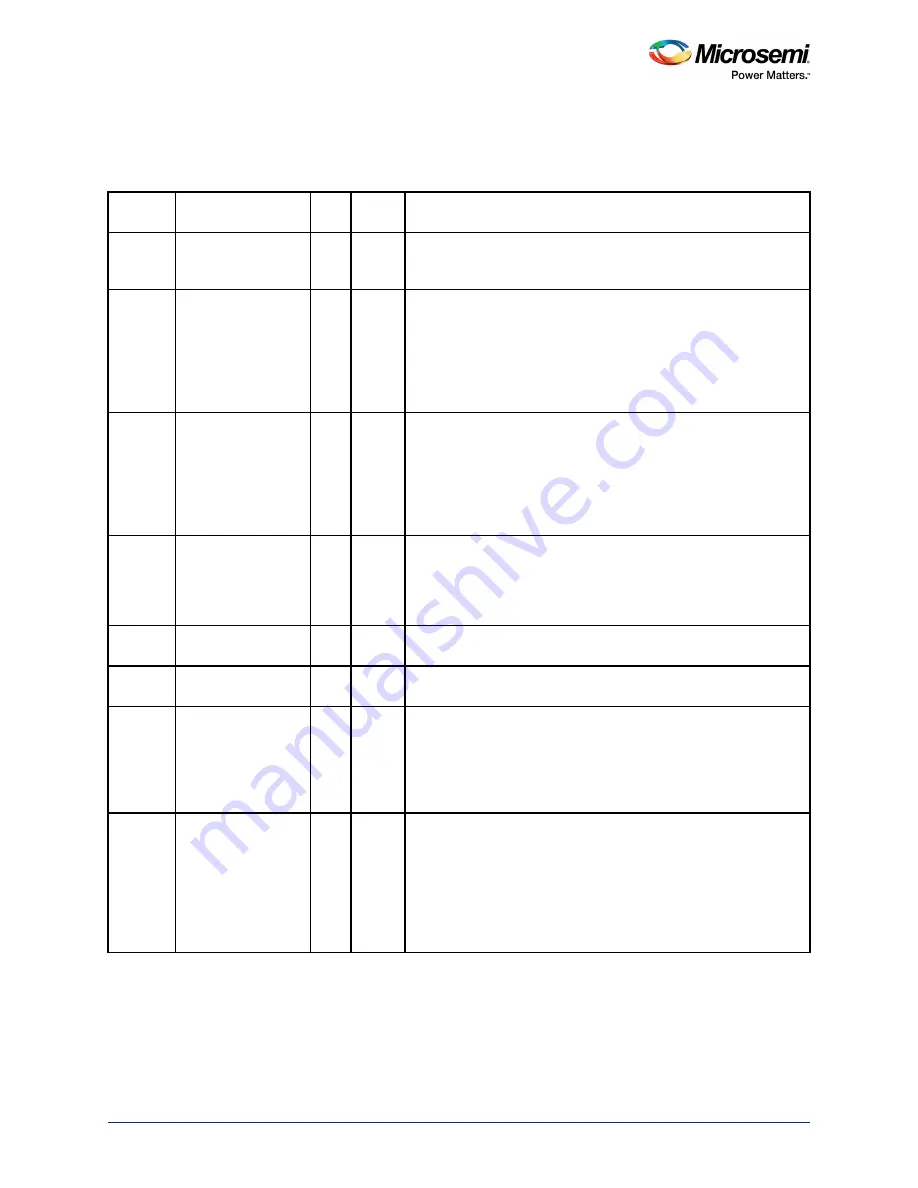

14.4.3.12 SPI Command Register

The following table describes the Command register..

Table 512 •

COMMAND

Bit

Number

Name

R/W

Reset

Value

Description

[31:7]

Reserved

R/W 0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

6

TXNOW

R/W 0

0: No effect

1: Writing one clears the TxBUSY bit in slave mode immediately

rather than waiting for PKTSIZE frames to be available, telling the

master that there is data available. This is intended to use when

less than the programmed PKTSIZE data frames are being

transmitted, removing the requirement to transmit PKTSIZE

frames. This bit stays set until the first data frame is transmitted.

5

AUTOSTALL

R/W

0: No effect

1: Writing one will cause the master to delay transmission until the

transmit FIFO contains the number of frames specified by the

register. This guarantee that the frames are transmitted

with no idle cycles or time gaps between them. This bit will be

automatically cleared as soon as the core starts transmitting the

frames.

4

CLRFRAMECNT

R/W

0: No effect

1: Writing one clears the internal frame counter. This bit always

reads as zero. The counter is also cleared when the core is

disabled, CTL1, or CTL2 are written (that is, the frame count limit

changed).

3

TXFIFORST

R/W 0

0: No effect

1: Writing one resets the Tx FIFO. This bit always reads as zero.

2

RXFIFORST

R/W 0

0: No effect

Writing one resets the Rx FIFO. This bit always reads as zero.

1

AUTOEMPTY

R/W 0

0: No effect

1: Writing one causes the SPI core to automatically discard any

further received data until the number of frames requested in the

FRAMECNT register has been received or (in slave mode) SSEL

goes inactive. This bit will stay set until all the frames are complete

or it is cleared.

0

AUTOFILL

R/W 0

0: No effect

1: Writing one causes the SPI core to automatically fill the transmit

FIFO with zeros to match the number of frames requested in the

FRAMECNT register. Typically, the five command bytes must be

written to the TxDATA register and then this bit must be set. Data

can be read from the receive FIFO until the complete set of frames

has been read. This bit will stay set until all the frames are

complete or it is cleared.