MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

56

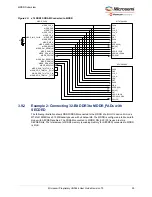

Figure 41 •

AXI Timing Optimization Logic

The AXI data lines into the DDR_FIC can now be relaxed with additional half AXI clock cycle as the AXI

valid signals are delayed by half AXI clock cycle. The following illustration shows the AXI transaction with

the optimization logic.

Figure 42 •

Timing Diagram

The following SDC constraints need to be added to the timing SDC file. It applies the proper timing

relaxation on the DDR_FIC_AXI signals.

For FDDR:

/* The following constraints provide a relaxation constraint on the signals of 1.5 clock periods.

The user should adjust the ddr_clock_frequency to match their application. */

set ddr_clock_frequency 333

set delay1 [ expr 3000/$ddr_clock_frequency ]

set_max_delay $delay1 -to [ get_pins { \

DDR_FIC_SUBSYSTEM_CLK

Fabric AXI

Master

MDDR/FDDR

DDR_FIC

WVALID

ARVALID

AWVALID

WREADY

ARREADY

FCCC

System Builder

Generated Component

Other AXI signals

AXI RESET

AWREADY

xVALID_new

Address/

data

AXI CLK

xVALID

xREADY

Data Transfer on

xVALID/xREADY

handshake