Page 16

Register Description

IF2008/PCIe / IF2008E

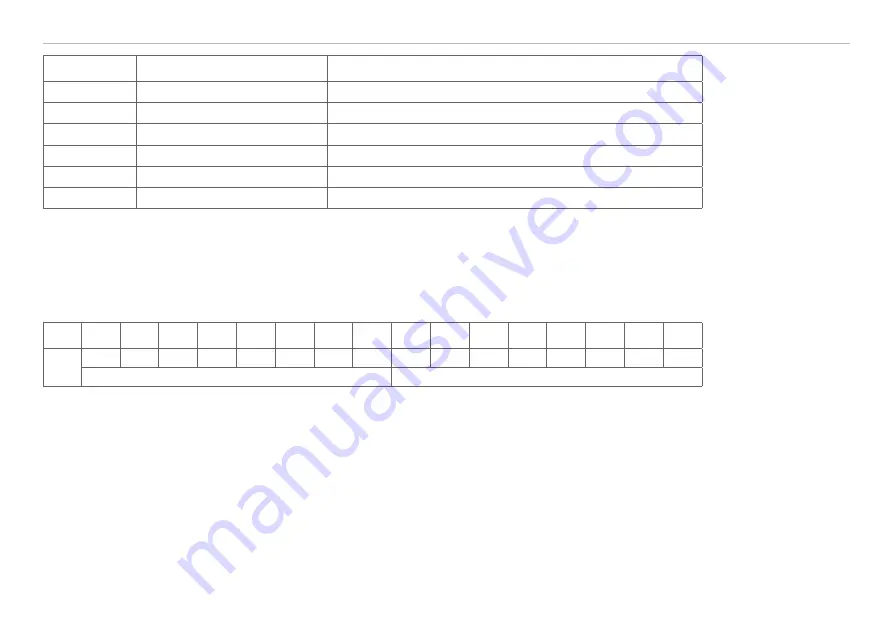

Base addr. + Write access

Read access

2Ch

Timer clock splitter

Timer clock splitter

2Eh

Output register

Output register

30h

Mode opto- and TxD outputs

Mode opto- and TxD outputs

32h

Trigger Outputs Mode

Mode trigger outputs, latch source and sensor power switch

34h

ADC control register

ADC-Kontrollregister

36h

Parity enable register

Parity error

Fig. 13: Local address assignment

10.

Register Description

10.1

Transmit Register

Base addr. + 00h (write access)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

S6

S5

S4

S3

S2

S1

D7

D6

D5

D4

D3

D2

D1

D0

Selection sensor channel

Data bits

Fig. 14: Transmit register

Bit 0 to 7

Include the data for the transmit register

Bit 8 to 15

Select the sensor channel

Bit 8 = 1

> Data are output on the sensor channel S1

Bit 9 = 1

> Data are output on the sensor channel S2

Bit 13 = 1

> Data are output on the sensor channel S6

Bit 14 ... 15 > free

Immediately on the write access to the address „0“, the data with the bit 8 to 13 selected sensor channel are transmitted. The baud

rate for the transmit register is automatically adapted to the selected sensor channel. In case that the data output is effected on more

channels, the baud rate of the best channel is used.