MAX32600 User’s Guide

Analog Front End

8.4 DAC

DAC Clock Enable / Clock Scaling

Each DAC instance runs from an independently scalable clock that is generated from the currently selected system clock source. Because this clock is used by the

APB and AHB interface logic as well as the internal DAC state machine logic, the clock must be enabled before attempting to access any of the DAC APB registers

or the AHB DAC FIFO.

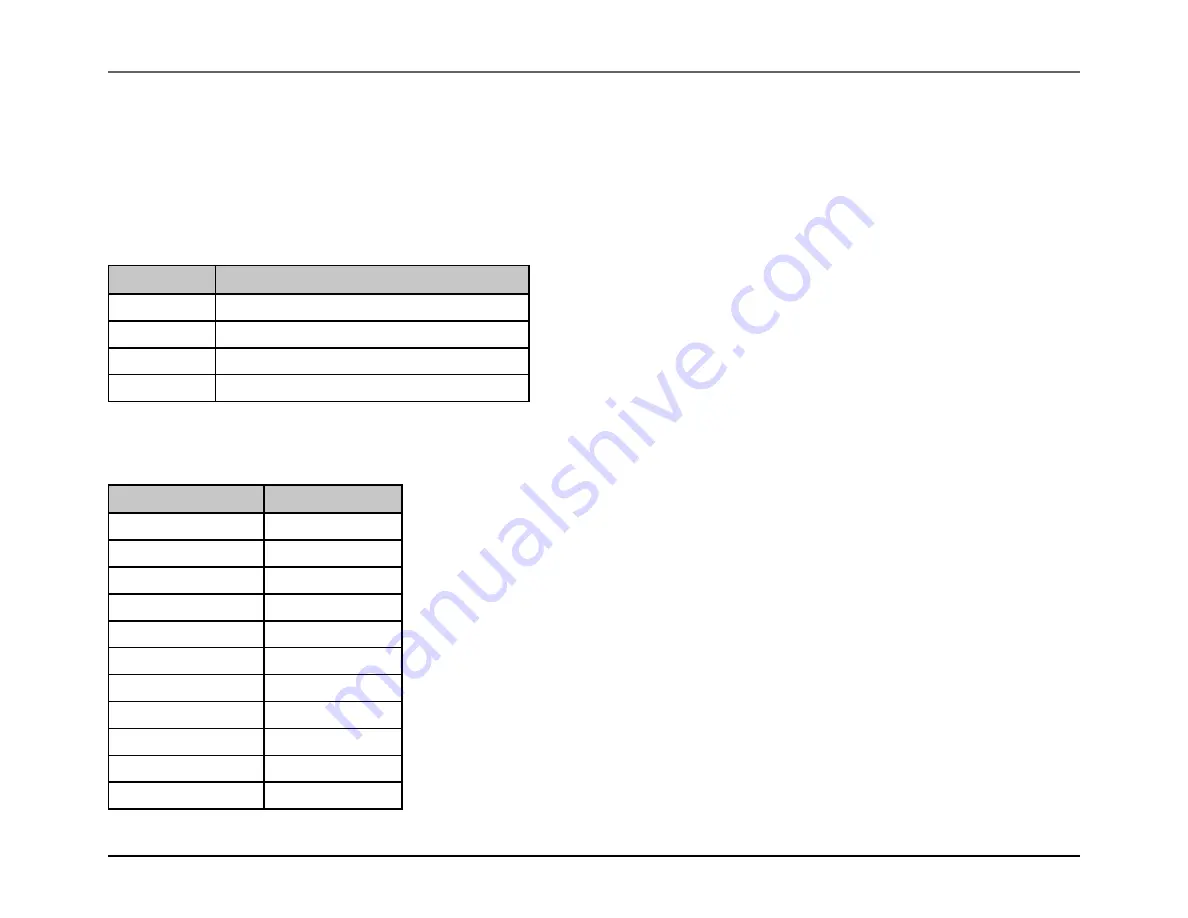

The clock enable / scaling setting is configured separately for each of the four DAC instances using registers in the Clock Manager module, as shown in the

below.

DAC Instance

Module Clock Scaling Register

0 (12-bit)

CLKMAN_CLK_CTRL_14_DAC0.dac0_clk_scale

1 (12-bit)

CLKMAN_CLK_CTRL_15_DAC1.dac1_clk_scale

2 (8-bit)

CLKMAN_CLK_CTRL_16_DAC2.dac2_clk_scale

3 (8-bit)

CLKMAN_CLK_CTRL_17_DAC3.dac3_clk_scale

Each of these registers contains a 4-bit

dac[n]_clk_scale

field which is used to enable the module clock for that DAC, and if desired, to scale the module clock

frequency by dividing it down from the system clock source, as detailed

dac[n]_clk_scale (4b)

DAC Clock Setting

0000b

Disabled

0001b

SysClkSource / 1

0010b

SysClkSource / 2

0011b

SysClkSource / 4

0100b

SysClkSource / 8

0101b

SysClkSource / 16

0110b

SysClkSource / 32

0111b

SysClkSource / 64

1000b

SysClkSource / 128

1001b

SysClkSource / 256

Other settings

Reserved

Rev.1.3 April 2015

Maxim Integrated

Page 455