6-4

Specifications

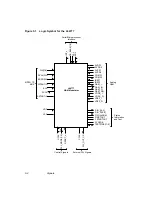

Figure 6.3

L64777 Bus 3-state Delay Timing

The numbers in column 1 of Table 6.4 refer to the timing parameters in

the preceding figures. All parameters in this table apply for T

A

= 0

°

C to

85

°

C, V

DD

= 3.1 V to 3.6 V, and an output load of 50 pF.

TN

DATA

11

11

Table 6.4

L64777 Preliminary Timing Parameters

No.

Parameter

Description

Min

Max

Unit

1

tCYCLE

Clock Cycle OCLK

32

–

ns

2

tPWH

Clock Pulse Width HIGH OCLK

7

–

ns

3

tPWL

Clock Pulse Width LOW OCLK

7

–

ns

4

tI_CYCLE

Clock Cycle ICLK

18.5

–

ns

5

tI_PWH

Clock Pulse Width HIGH ICLK

9

–

ns

6

tI_PWL

Clock Pulse Width LOW ICLK

9

–

ns

7

tI_S

Input Setup Time to ICLK

6

–

ns

8

tI_H

Input Hold to ICLK

2

–

ns

9

tRWH

Reset Pulse Width HIGH

50

–

ns

10

tWK

Wake-up Time after RESET

(used for RAM initialization during

microprocessor configuration

access)

1280

2560

–

–

ICLK cycles with

DVALIDIN =

HIGH

OCLK cycles

11

tTDLY

Delay from TN

–

20

ns

Summary of Contents for L64777

Page 1: ...L64777 DVB QAM Modulator Order Number I14031 A Technical Manual June 2000...

Page 10: ...x Contents...

Page 14: ...1 4 Introduction...

Page 90: ...5 10 Signals...

Page 110: ...A 8 Programming the L64777 in Serial Host Interface Mode...

Page 116: ...C 2 Monitoring Device Internal Signals...

Page 124: ......