- 10 -

Copyright ©

LG Electronics Inc. All rights reserved.

Only for training and service purposes.

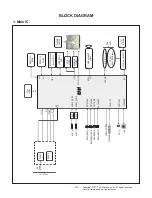

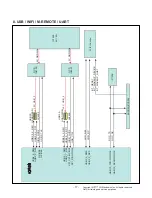

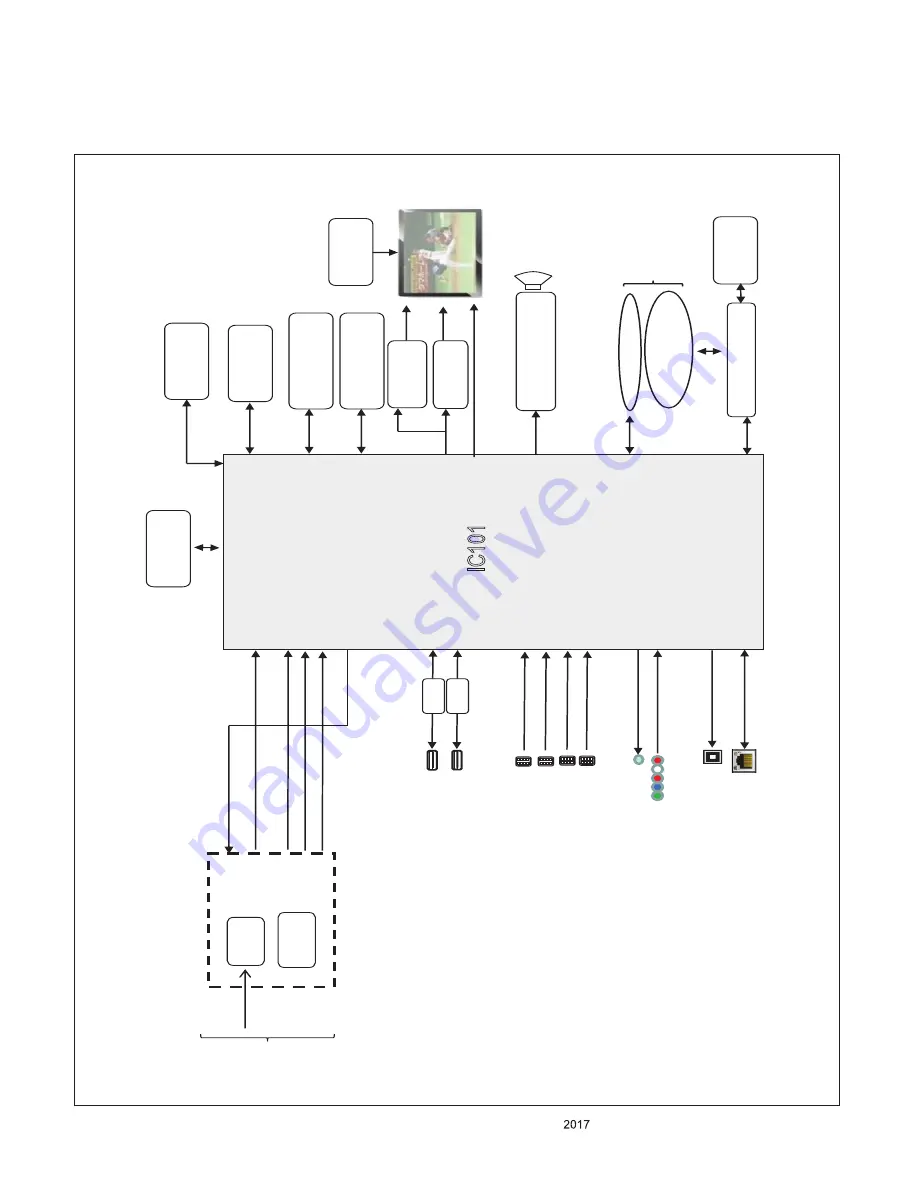

BLOCK DIAGRAM

1. Main IC

MAIN

Audio

AM

P

IC5800

IC

10

1

IF+,

IF

-

OPTIC

LA

N

HDMI1

HDMI 2.

0

EEPROM(NVRAM)

(256Kb

) IC10

2

PHY3

_RX0

N

Air/

Cable

TUNE

R

(C/A

)

DEMO

D

USB1

(2.0

)

eMMC

IC8800

(4GB

)

Sub

Mico

m

(IC3000)

P_TS

X_TA

L

24MHz

X_TA

L

32.768K

Hz

I2S Ou

t

I2C

0

I2C

4

R E A R

YPbP

r

SPDIF

OU

T

ETHERNET

I2C

1

SU

B

ASSY

IR

/ KE

Y

LOGO

LIGHT(Ready)

WIFI/BT

Comb

o

USB_WIFI

CVBS

HDMI3

HDMI 2.

0

USB2

(2.0

)

RS2

32C/HP

HDMI2(ARC)

HDMI

2.0

AV

EPI

3G

/1.5

G

OC

P

OC

P

USB2

.0_2_DM1

USB2

.0_3_DM0

PHY2

_RX0

N

PHY1

_RX0

N

I2C6

SI

F

HDMI4

HDMI 2.

0

PHY0

_RX0

N

PMIC

(IC9200)

GA

MMA

IC

(IC9400)

CVBS/COM

P

M0

M1

DDR3

213

3

512M

B

DDR3

213

3

256M

B

I2C

5

Sub PMIC

(IC9300)

Summary of Contents for 43UJ6300

Page 95: ......