MIPI D-PHY Bandwidth Matrix Table

User Guide

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

14

FPGA-UG-02041-1.1

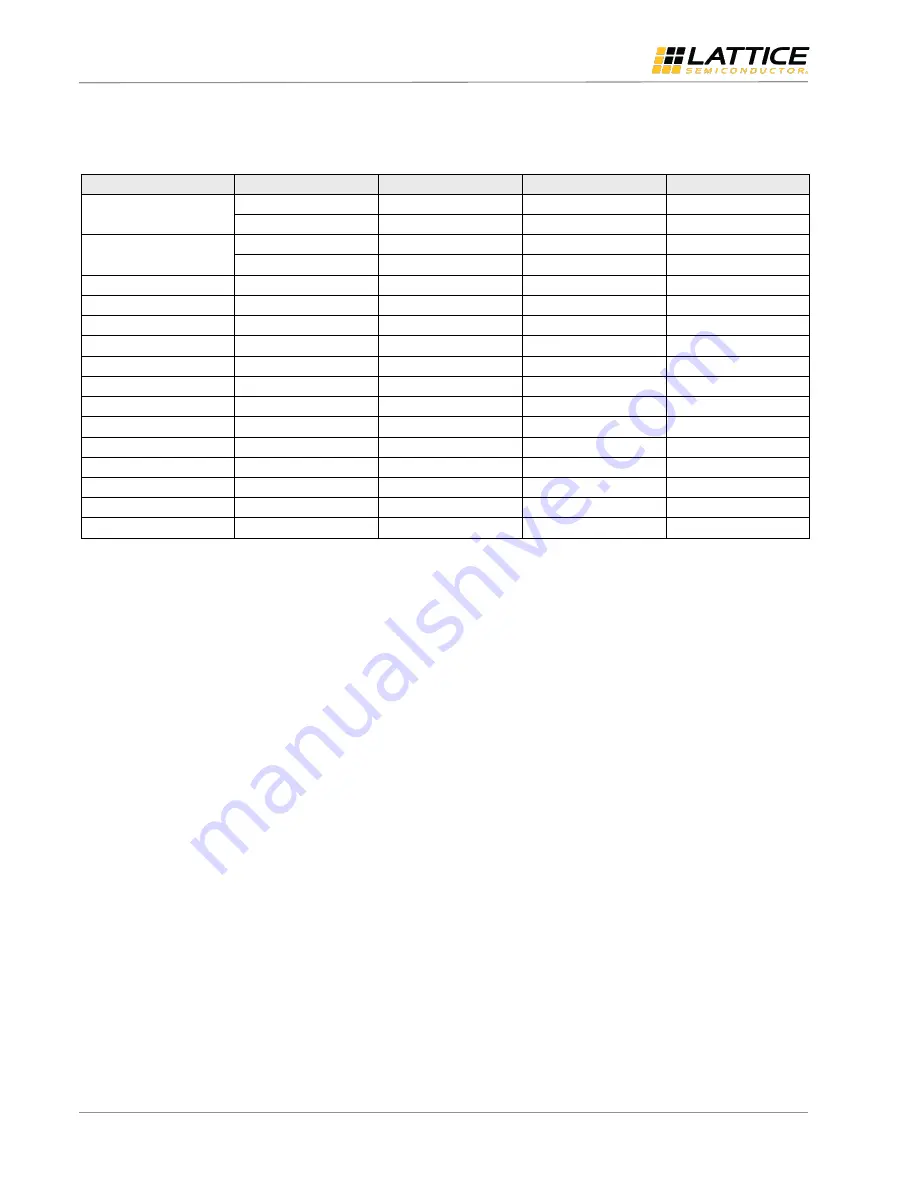

specifies the packet size constraints for the supported data formats. The length of each packet must be a

multiple of the values in the table. For simplicity, all data format examples are single lane configurations.

Table 4.1. CSI-2 Packet Size Constraints*

Data Format

Odd/Even Lines

Pixels

Bytes

Bits

YUV420 8-bit

Odd

2

2

16

Even

2

4

32

YUV420 10-bit

Odd

4

5

40

Even

4

10

80

YUV422 8-bit

—

2

4

32

YUV422 10-bit

—

2

5

40

RGB888

—

1

3

24

RGB666

—

4

9

72

RGB565

—

1

2

16

RGB555

—

1

2

16

RGB444

—

1

2

16

RAW6

—

4

3

24

RAW7

—

8

7

56

RAW8

—

1

1

8

RAW10

—

4

5

40

RAW12

—

2

3

24

RAW14

—

4

7

56

*Note

: RGB555 and RGB444 data should be made to look like RGB565 data by inserting padding bits to the LSBs of each color

component.

4.1.

xMulti-lane

MIPI CSI-2 is lane-scalable. Applications requiring more bandwidth than that provided by one data lane, or those trying

to avoid high clock rates, can expand the data path to two, three, or four lanes wide and obtain approximately linear

increases in peak bus bandwidth