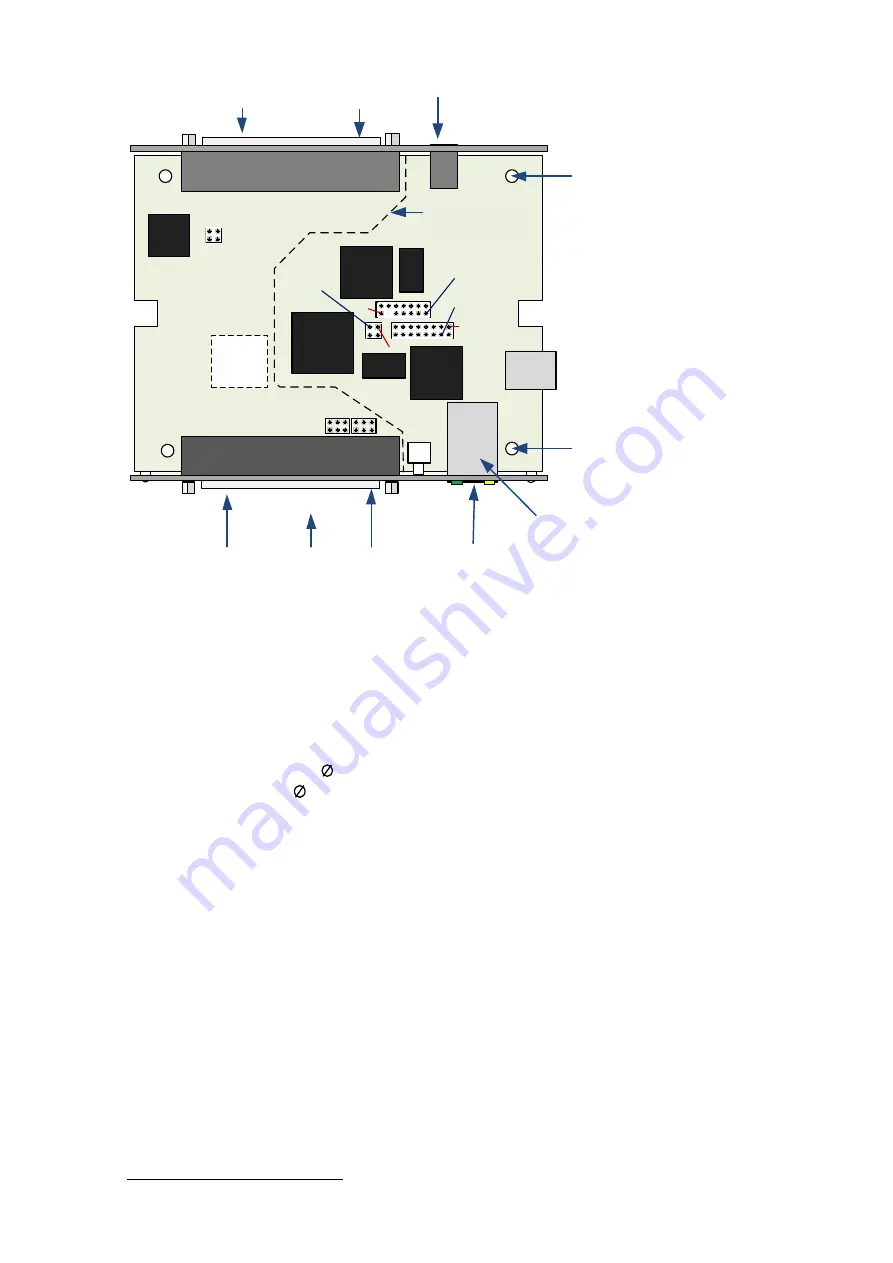

Fig. 4-2: The location of the "common wires" circuits on the E-502 board

In particular, GND is a common wire for internal interfaces UART, JTAG Blackfin, JTAG

ARM.

If you use a separate E-502 board without a chassis

in the embedded chassis circuit applications

(CHASSIS), it is recommended to connect it to the solid metal surface of the chassis (case

construction). Two right ports of

3.05 mm on fig. 4-2 have a metal coating connected to a CHASSIS

circuit, and two left ports of 3.05 mm are isolated from the other circuits. These 4 mounting ports

are used to secure the E-502 board.

4.4. E-502 connectors description

4.4.1. Connector

Analog

.

Connector Analog is a 37-pin 2-row type DRB-37M plug on the front panel of the E-502. The

conductive connector contact piece (shield) is electrically connected to the GND signal ground

circuit. On the shield of the cable part of the connector, the shield of the signal cable can be directly

sealed. The connector

Analog

shield does not have a contact with AGND, DGND and other circuits

of the

Analog

connector.

3

Here we do not consider the usage accuracy of the certified Measuring Device without a standard chassis.

1

JTAG Blackfin

(

GND

)

JTAG ARM

(

GND

)

1

1

UART

(

GND

)

ADSP-

BF523

FPGA

Cyclone

IV

SDRAM

SDRAM

ARM

LPC4337

CPLD

USB

(

GND_USB

)

D I G I T A L

Элементы

ЦАП

A N A L O G

Гальванический

барьер

Отв

. 3,05

мм

GHASSIS

Корпус

разъёма

(

CHASSIS

)

Корпус

разъёма

(

CHASSIS

)

Цифровые

сигналы

(

DGND

)

DI_SYN1

(

DGND

)

A

налоговые

сигналы

(

AGND

)

Изололированные

входы

Ethernet

GHASSIS

Отв

. 3,05

мм

GHASSIS

0 V

DAC

elements

Digital signals

Port Ø3,05 mm

Port Ø3,05 mm

Connector

chassis

Isolated Ethernet

inputs

Galvanic barrier

Connector

chassis

Analog

signals

Summary of Contents for ADC Series

Page 66: ...7 2 Front panel draft 7 3 Back panel draft 2 ports of 5 5...

Page 69: ......