30

Operation Theory

Software Conversion with Polling Data Transfer

Acquisition Mode (Software Polling)

Considered the most convenient way to acquire a single A/D data,

the A/D converter starts one conversion whenever the dedicated

software command is executed. The software then polls the

conversion status and reads back the A/D data when it is

available.

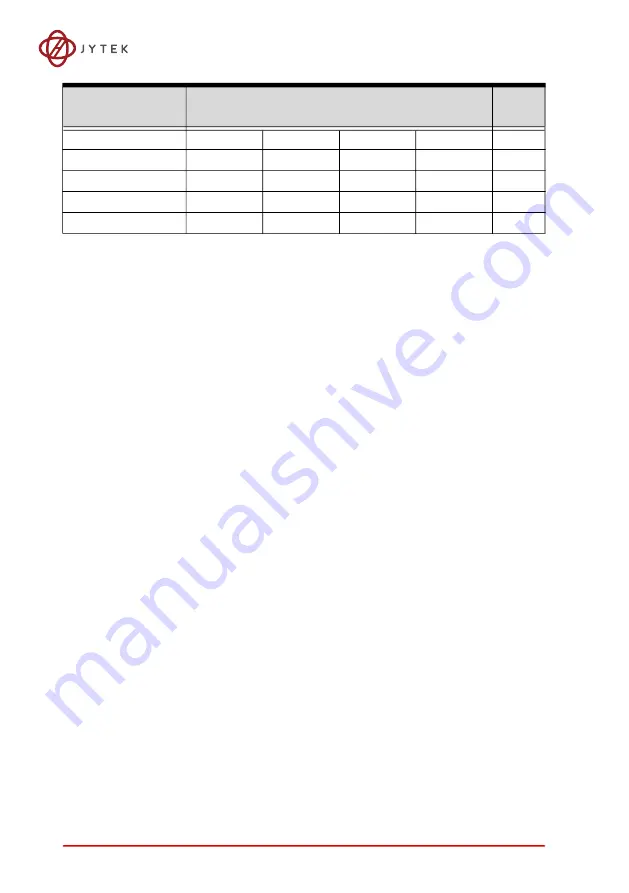

FSR-1LSB

1.249961V 0.999969V 0.499984V 0.249992V

7FFF

Mi1LSB

38.14uV

30.51uV

15.25uV

7.62uV

0001

Midscale

0V

0V

0V

0V

0000

Midscale -1LSB

-38.14uV

-30.51uV

-15.25uV

-7.62uV

FFFF

-FSR

-1.25V

-1V

-0.5V

-0.25V

8000

Description

Bipolar Analog Input Range

Digital

code

Table 4-2: Bipolar Analog Input Range and Output Digital Code

Summary of Contents for NuDAQ PCI-69222

Page 4: ......

Page 10: ...vi...

Page 34: ...24 Hardware Information...

Page 74: ...64 Operation Theory...

Page 80: ...70 Getting Service...