KS-FX8R

1-22

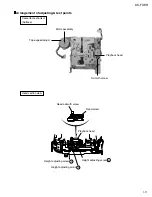

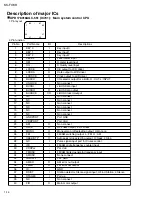

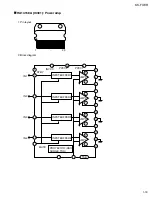

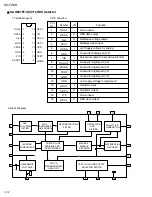

3.Block Diagram

ANI-

ALLUDING

FILTER

5kHz

BAND PASS

(8th ORDER)

RECONSTRUCTION

FILTER

OSCILLATOR

AND

DIVIDER

DUALITY BIT

GENERATOR

CLOCKED

COMPARATOR

COSTAS LOOP

VARIABLE AND

FIXWD DIVIDER

BIPHASE

SYMBOL

DECODER

DIFFERENTIAL

DECODER

REFERENCE

VOLTAGE

CLOCK

REGENERATION

AND SYNC

TEST LOGIC AND OUTPUT

SELECTOR SWITCH

11

10

15

16

12

14

13

9

2

1

3

5

7

8

4

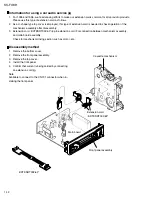

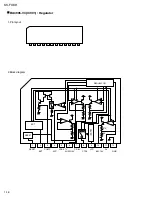

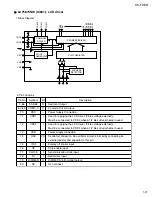

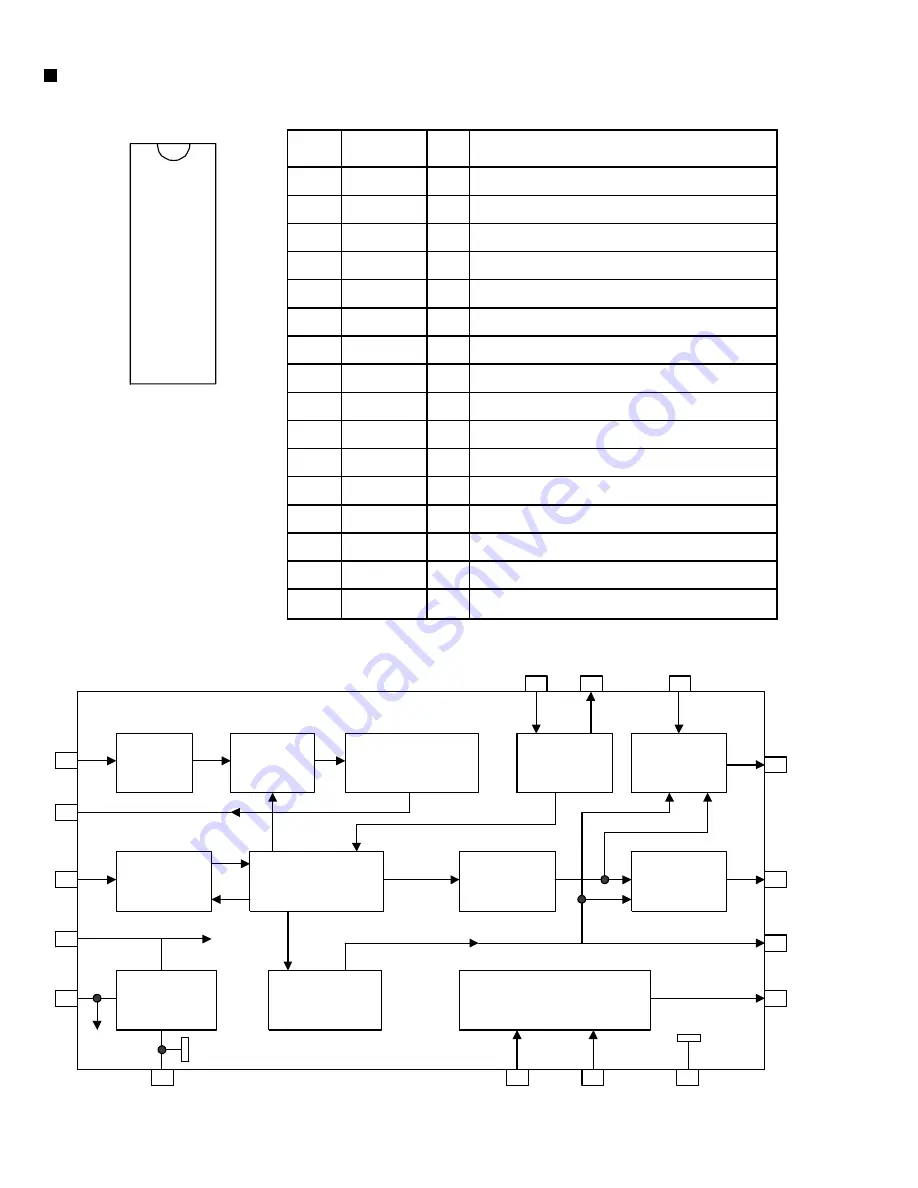

1.Terminal Layout

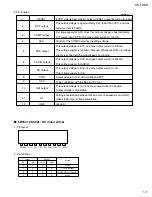

2.Pin Function

6

SAA6579T-X(IC71):RDS detector

QUAL

RDDA

Vref

MUX

VDDA

GND

CIN

SCOUT

RDCL

T75

OSCO

OSC1

VDD

GND

TEST

MODE

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

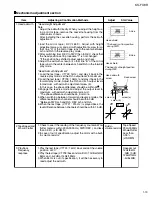

QUAL

RDDA

Vref

MUX

VDDA

GND

CIN

SCOUT

MODE

TEST

GND

VDD

OSC1

OSC0

T75

RDCL

-

O

O

I

-

-

I

O

-

-

-

-

I

O

-

O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Non connect

RDS data output

Reference voltage output

Multiplex signal input

+5V Supply voltage for analog

Ground for analog part (0V)

Sub carrier output of reconstruction filter

Ground for digital part (0V)

Ground for digital part (0V)

Ground for digital part (0V)

Ground for digital part (0V)

+5V supply voltage for digital part

Oscillator input

Oscillator output

Non connect

RDS clock output

Function

I/O

Symbol

Pin

No.