2-7(No.YF146)

ZOOMSW

SCPU_SI

REG_CS

FLSH_RST

AUDIO_CS

OSD_CS

3AAZEROG

ANA_CLK

CHRG_EVR

UNREGCHK

SBT5

A_MUTE

PD_L

KEY_ACH

PMEDIA

DIAL_OFF

ANA_IN

ADP_L

T_BATT

CHRGLED

DIAL_REC

ANA_OUT

ANA_CLK

SCPU_CS

KEY_BCH

DIAL_REC

I_MTR

CHRG_EVR

DIAL_PB

MONI_SW

DC_CHEK

DIAL_OFF

PMEDIA

SBD5

ANA_OUT

DIAL_PB

IR_RMC

V_BATT

EEPRM_DI

EEPRM_CS

LCDRVS

SDET

LCDRVS

SETSW

KEY_CCH

LCD_CTL

ANA_CLK

LCD_CTL

ACESLED

ZGH_THRU

ANA_CS

SCPU_SO

LCD_CS

L_MUTE

REG_CS

HOSTLED

TG2_RST

EEPRM_CK

EEPRM_DO

PDET

SBD5

PS_ZEROG

DBATT

SCPU_SCK

ANA_OUT

PSCTL

ZGH_OUT

DC_CHEK

ANA_RST

DBATT

INFOSW

SBT5

LCD_CS

ISO200

R1020

1K

SJIG_RX

BUZZER

C1025

0.1

R1008

1K

ANA_OUT

R1010

680

REC_SW

C1004

0.1

L1002

10u

KEY_A

DATA_OUT

R1005

2.2K

R1022

1k

Q1001

DTC124EE-X

R1054

47k

SBD5

C1046 0.1

IC1001

MN102H60GJD

91

LCD_BL

89

S_DET

31

DIAL_PB

32

DIAL_OFF

DIAL_REC

30

5

CHRG_EVR

35

DC_CHEK

42

MODE_SW/P_MEDIA

12

WORD

82

RESET

19

VSS

2

XI

2

MODE

92

VSS

73

SBD5

74

SBT5

88

P_DET

95

D_BATT

49

ISO200

27

FLSH_RST

71

ANA_IN

72

ANA_OUT

70

ANA_CLK

55

RXD

56

TXD

97 EEP_CS

51 SCPU_IN

52 SCPU_OUT

50 SCPU_CLK

68 DATA_IN

69 DATA_OUT

67 CLK_OUT

79 SCPU_CS

22 VDD

28 RTC_CS

1

REG_CS

39 OSD_CS

14 EEP_IN

15 EEP_OUT

13 EEP_CLK

9

ANA_CS

93 BZ_FREQ

94 BZ_ENV

90 ANA_RST

10 SYTG_RST

2

LCD_CS

17 VDD

6

LCD_RVS

84 PS_CTL

R1057

100k

R1001

100k

ANA_CLK

REG_CS

CHRG_LED

R1007

4.7k

R1009

680

LCD_CTL

IC1002

RS5C314-X

8

VDD

7

XIN

6

XOUT

5

INTR

4 VSS

3 SIO

2 CLK

1 CS

R1055

10k

A_MUTE

C1026

0.1

CLK_OUT

ADP_L

R1006

4.7k

PD_L

SJIG_TX

C1006

7p

PS_ZEROG

R1058

100k

SET_SW

V_BATT

ANA_CLK

D_BATT

R1056

4.7k

SJIG_RST

PLAY_SW

R1028

1k

3AAZEROG

L_MUTE

GND

ZOOM_SW

R1051

2.7k

R1062

100k

D1001

DA221-X

2

1

3

R1036

OPEN

P_MEDIA

Q1002

2SC4617/QR/-X

R1024

1k

R1083

100k

REG_3.1V

T_BATT

R1017

1k

X1002

NAX0564-001X

IC1005

SN74AHC1G04DC-X

123

4

5

D1002

1SS376-X

LCD_CS

INFO_SW

Q1003

DTA124EE-X

R1052

18k

R1018

1k

R1053

150k

UNREGCHK

KEY_B

POFF_SW

IC1004

SN74AHC1G08DC-X

74AHC1G08GW-X

1

2

3

45

T

C1005

10/6.3

Q1004

2SC5658/QRS/-X

CHRG_EVR

C1031

1

R1014

OPEN

ZGH_THRU

ACES_LED

C1044

0.01

R1031

1k

DC_CHEK

LCD_RVS

R1016

2.2k

KEY_C

L1001

NQR0129-002x

R1061

100k

R1060

100k

R1003

2.2K

D1003

OPEN

SBT5

LIT_3V

WORD

ANA_OUT

AUDIO_CS

AL_3.1V

R1023

1k

LCD_OPEN

R1015

OPEN

R1059

100k

IR_RMC

R1063 47k

HOST_LED

R1025

1k

Q1006

DTA124EE-X

R1019

1k

R1004

2.2K

N

IC1003

S-80827CNNB-G-W

1

OUT

2

DET

3

4

VSS

R1082

100k

R1064 1k

R1030

1k

ZGH_OUT

I_MTR

R1029

1k

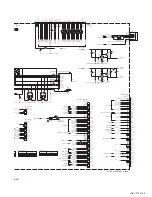

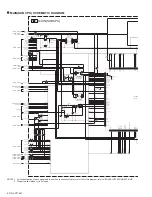

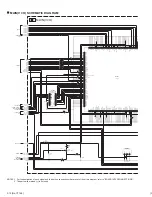

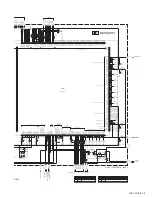

MAIN(SUB CPU)

1

0

TO MAIN IF(CN101)

TO MAIN IF(CN103)

TO MAIN IF(CN110)

TO MAIN IF(CN101,

103,110)

TO MAIN IF(CN110)

TO MAIN IF(CN103)

TO MAIN IF(CN101),

AUDIO,V I/O

TO MAIN IF(CN101),

AUDIO,V I/O

TO MAIN IF(CN101)

TO AUDIO

TO MAIN IF(CN101)

TO MAIN IF(CN121)

TO MAIN IF(CN101)

TO MAIN IF(CN104)

TO MAIN IF(CN101)

TO MAIN IF(CN103)

TO MAIN IF(CN101)

TO MAIN IF(IC171)

TO MAIN IF(CN101,

103,110,IC121)

MAIN(SUB CPU) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.