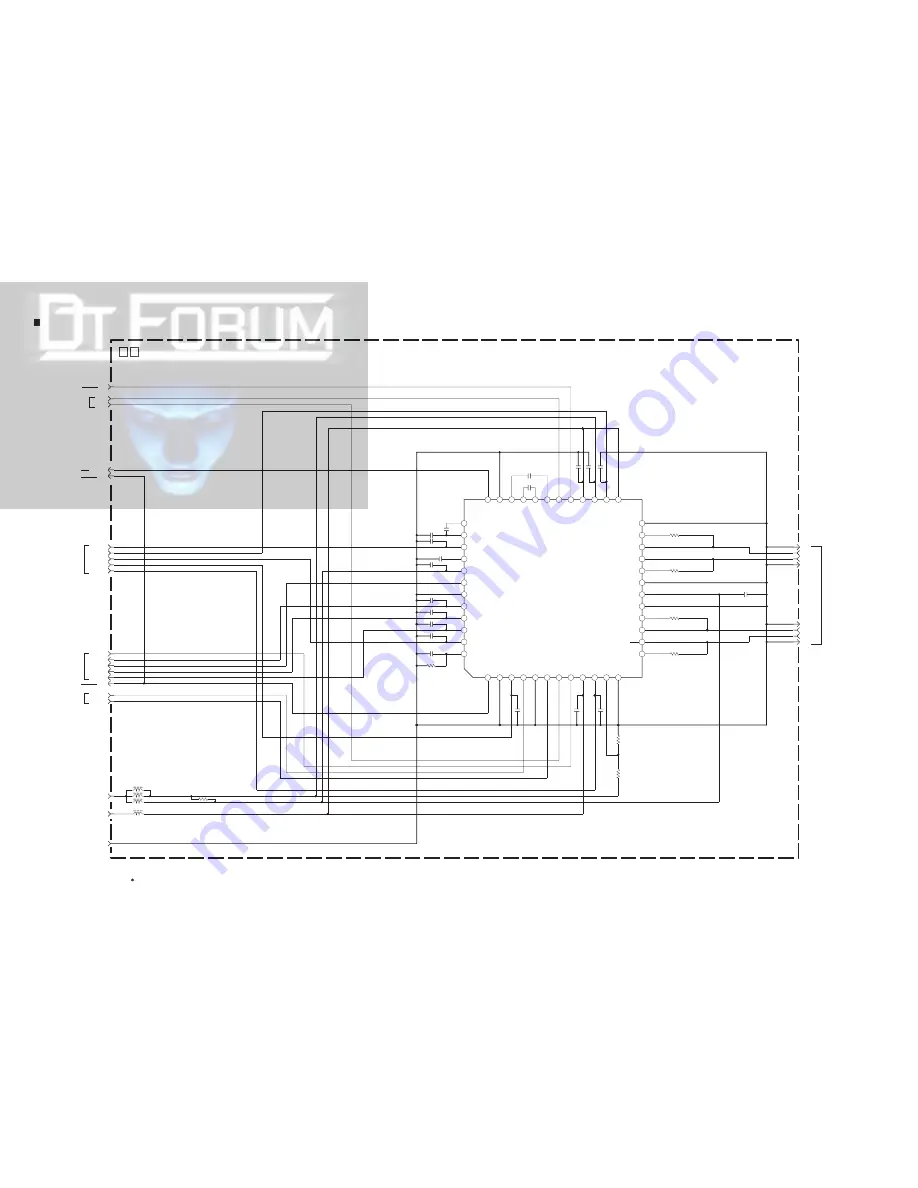

(No.YF219)2-15

2-16(No.YF219)

yf219_y20444001a_rev0.1

MAIN(PRE/REC)

1

0

REG_2.8V

REG_4.65V_L3504

REG_4.65V

REG_4.65V_L3505

REG_2.8V_L3501

REC_CLK

C3517

0.01

C3518

0.01

C3519

0.1

C3514

0.01

OPEN

C3516

0.01

C3502

10

C3515

0.01

OPEN

C3513

0.01

C3510

0.01

C3503

0.01

C3505

0.01

C3506

10

C3507

0.1

C3512

0.01

C3504

0.01

C3509

470p

C3508

470p

C3501

0.01

CH

C3511

68pF

IC3501

LA70054W

1

ATF_OUT

2

ATF_GND

3

NOSIG_EVR

4

REC_DATA

5

REC_GND

6

REC_CLK

7

REC_H

8

REC_CTL

9

Vcc2.8

10

REC_GAIN

11

REC_MONI

12

HEAD_GND

13

DY1

14

Y1

15

X1

16

DX1

17

HEAD_GND

18

HEAD_VCC

19

HEAD_GND

20

DY2

21

Y2

22

X2

23

DX2

24

HEAD_GND

25

HID1_INV

26

DUMP1

27

PRE_VCC

28

VDD

29

HID1

30

PB_H

31

PB2CH_OUT

32

PB1CH_OUT

33

PB1CH_IN

34

PB2CH_IN

35

PB_GND

36

PB_MONI

37

PB_OUT

38

PB_IN

39

AGC_CTL

40

AGC_DET

41

Vcc4.8

42

AGC_OUT

43

MAIN_GND

44

REG_1.1V

45

VRB_AGC

46

VRB_ATF

47

ATF_GAIN

48

REG_FIL

L3505

NQR0602-001X

L3502

OPEN

L3501

NQR0602-001X

L3504

OPEN

R3509

150

R3530

R3519

OPEN

R3518

OPEN

R3508

150

R3535

470k

OPEN

R3507

150

R3506

150

REC_CLK

ATF_GAIN

2S

2F

1F

REG_2.8V

REG_4.65V

GND

NOSIG_LV

DUMP_CTL

AGC_CTL

HID

TO MAIN IF(CN111),

CPU,PARAGON3

PBH

RECH

REC_CTL

REC_DATA

1S

REC_ADJ

GND

TO MAIN IF

(CN3501)

GND

GND

VREF_1.1

AGC_OUT

VRB_AGC

VRB_ATF

ATFI

ATFI

ENV_OUT

GND

0

Ω

TO MAIN IF(CN111)

TO MAIN IF(CN111).

PARAGON3

TO MAIN IF(CN111).

PARAGON3

TO CPU

TO PARAGON3

TO PARAGON3

TO PARAGON3

MAIN(PRE/REC) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.