Data Sheet: JN5142

IEEE802.15.4 Wireless Microcontroller

© NXP Laboratories UK 2012

JN-DS-JN5142 1v0

1

Overview

Features: Transceiver

2.4GHz IEEE802.15.4 compliant

128-bit AES security processor

MAC accelerator with packet

formatting, CRCs, address check,

auto-acks, timers

Integrated ultra low power sleep

oscillator

– 0.5µA

2.0V to 3.6V battery operation

Deep sleep current 0.12µA

(Wake-up from IO)

0.5µA sleep with timer (1.5uA with

RAM held)

<$0.50 external component cost

Rx current 16.5mA

Tx current 14.8mA

Receiver sensitivity -95dBm

Transmit power 2.5dBm

Features: Microcontroller

32-bit RISC CPU, 1 to 32MHz

clock speed

Low power operation

Variable instruction width for high

coding efficiency

Multi-stage instruction pipeline

128KB ROM and 32KB RAM for

bootloaded program code

RF4CE or JenNet-IP software in

ROM

Master/Slave I2C interface.

3xPWM and Application

timer/counter

UART

SPI port with 3 selects

Supply Voltage Monitor with 8

programmable thresholds

2- to 4-input 8-bit ADC,

comparator

Battery and temperature sensors

Watchdog timer and Power-on-

Reset (with brown-out) circuit

Up to 18 DIO

Industrial temp -40°C to +125°C

6x6mm 40-lead Punched QFN

Lead-free and RoHS compliant

The JN5142 is an ultra low power, high performance wireless

microcontroller suitable for Remote Control, IEEE802.15.4 and Active RFID

applications. There is also a ROM variant that supports JenNet-IP Smart

Devices. The JN5142 features an enhanced 32-bit RISC processor offering

high coding efficiency through variable width instructions, a multi-stage

instruction pipeline and low power operation with programmable clock

speeds. It also includes a 2.4GHz IEEE802.15.4 compliant transceiver,

128KB of ROM, 32KB of RAM, and a comprehensive mix of analogue and

digital peripherals. The operating current is below 18mA, allowing operation

direct from a coin cell.

The peripherals support a wide range of applications. They include a 2-wire

serial interface, which operates as either master or slave, a two channel

ADC with battery and temperature sensors. A large switch matrix of up to 81

elements can be supported for remote control applications. The best in

class radio current and a 0.5µA sleep timer give excellent battery life.

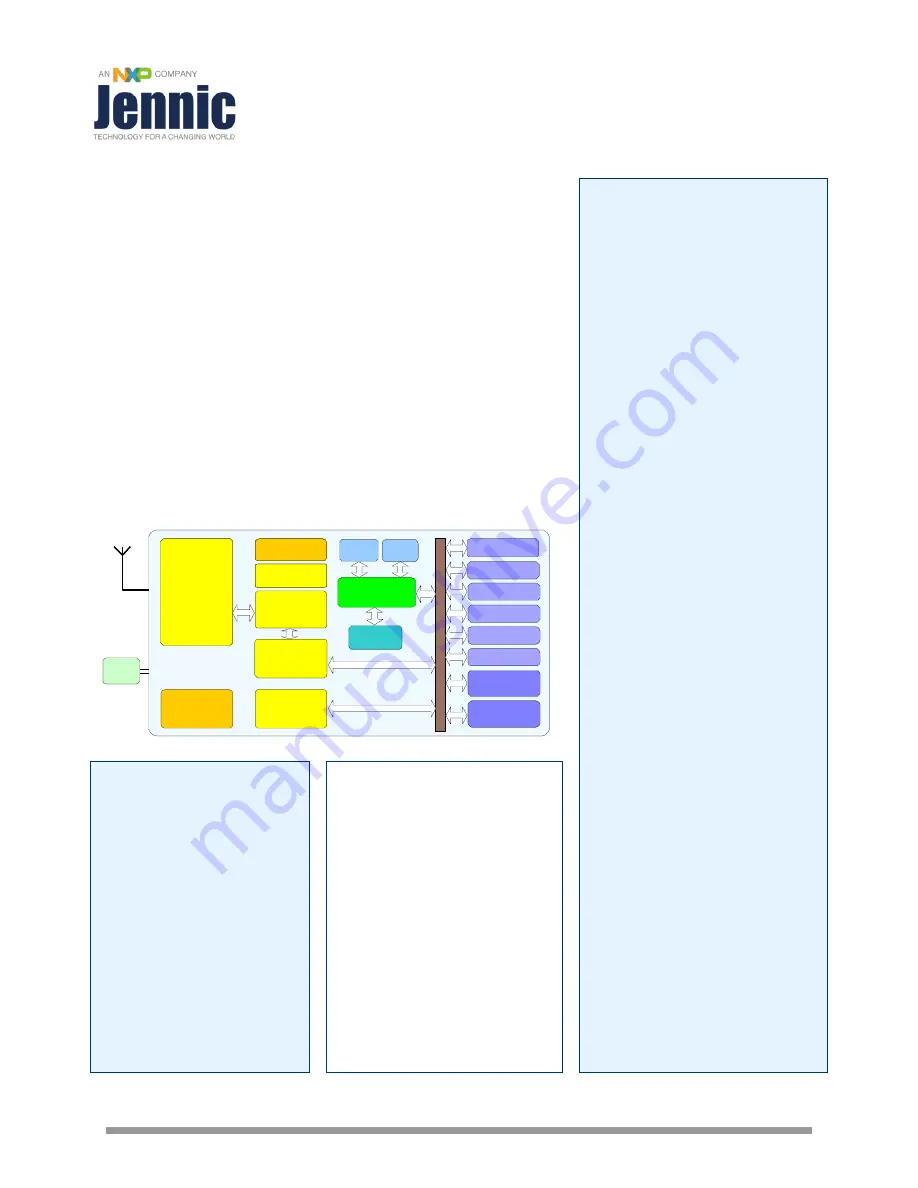

Block Diagram

32-bit

RISC CPU

Timer

UART

4-Chan 8-bit

ADC

Battery and,

Temp Sensors

2-Wire Serial

(Master)

SPI

128-bit AES

Encryption

Accelerator

2.4GH

z

Radio

2.4GHz

Radio

ROM

128KB

Power

Management

XTAL

O-QPSK

Modem

29-byte

OTP eFuse

2-Wire Serial

(Slave)

Sleep Counter

Watchdog

Timer

Watchdog

Timer

Voltage Supply

Monitor

RAM

32KB

IEEE802.15.4

MAC

Accelerator

Benefits

Single chip optimized for

simple applications

Very low current solution for

long battery life

– over 10 yrs

RF4CE in ROM

Variant for JenNet-IP Smart

Devices

Highly featured 32-bit RISC

CPU for high performance

and low power

System BOM is low in

component count and cost

Flexible sensor interfacing

options

Applications

Robust and secure low power

wireless applications using

RF4CE

Remote Control

Toys and gaming peripherals

Active RFID tags

Point-to-point or star networks

using IEEE802.15.4

Energy harvesting, for example

self powered light switch

Smart Lighting Networks

Building Automation