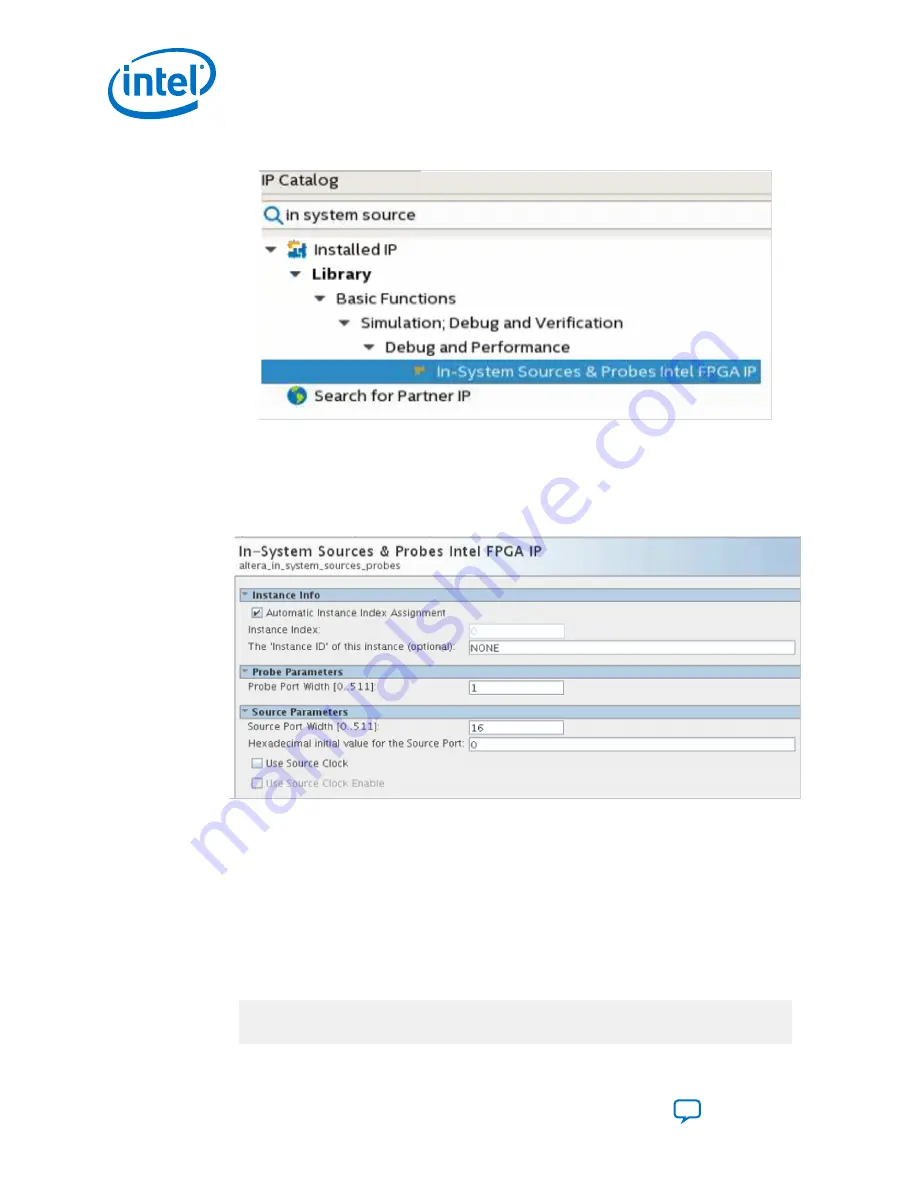

Figure 112. IP Catalog Search Field

2. Double-click In-System Sources & Probes Intel FPGA IP.

3. Name the IP,

src

4. Configure the IP with these settings.

Figure 113. In-System Source & Probes Intel FPGA IP Configuration

Related Information

Making the Top Level Connection

on page 224

B.6. Making the Top Level Connection

Follow this procedure to make your top level connection through RTL.

1. Click File > New then select Verilog HDL File.

2. Write the RTL code to connect the blocks.

module pam4_12ch(

input wire pll_refclk0, // pll_refclk0.clk

input wire reset,

B. PMA Direct PAM4 30 Gbps to 57.8 Gbps Implementation

UG-20056 | 2019.02.04

Intel

®

Stratix

®

10 E-Tile Transceiver PHY User Guide

224