6-1

CHAPTER 6

INTERRUPT SYSTEM

6.1

OVERVIEW

The 8XC251Sx, like other control-oriented computer architectures, employs a program interrupt

method. This operation branches to a subroutine and performs some service in response to the

interrupt. When the subroutine completes, execution resumes at the point where the interrupt oc-

curred. Interrupts may occur as a result of internal 8XC251Sx activity (e.g., timer overflow) or at

the initiation of electrical signals external to the microcontroller (e.g., serial port communication).

In all cases, interrupt operation is programmed by the system designer, who determines priority

of interrupt service relative to normal code execution and other interrupt service routines. Seven

of the eight interrupts are enabled or disabled by the system designer and may be manipulated

dynamically.

A typical interrupt event chain occurs as follows. An internal or external device initiates an inter-

rupt-request signal. This signal, connected to an input pin (see Table 6-1) and periodically sam-

pled by the 8XC251Sx, latches the event into a flag buffer. The priority of the flag (see Table 6-2,

Interrupt System Special Function Registers) is compared to the priority of other interrupts by the

interrupt handler. A high priority causes the handler to set an interrupt flag. This signals the in-

struction execution unit to execute a context switch. This context switch breaks the current flow

of instruction sequences. The execution unit completes the current instruction prior to a save of

the program counter (PC) and reloads the PC with the start address of a software service routine.

The software service routine executes assigned tasks and as a final activity performs a RETI (re-

turn from interrupt) instruction. This instruction signals completion of the interrupt, resets the in-

terrupt-in-progress priority, and reloads the program counter. Program operation then continues

from the original point of interruption.

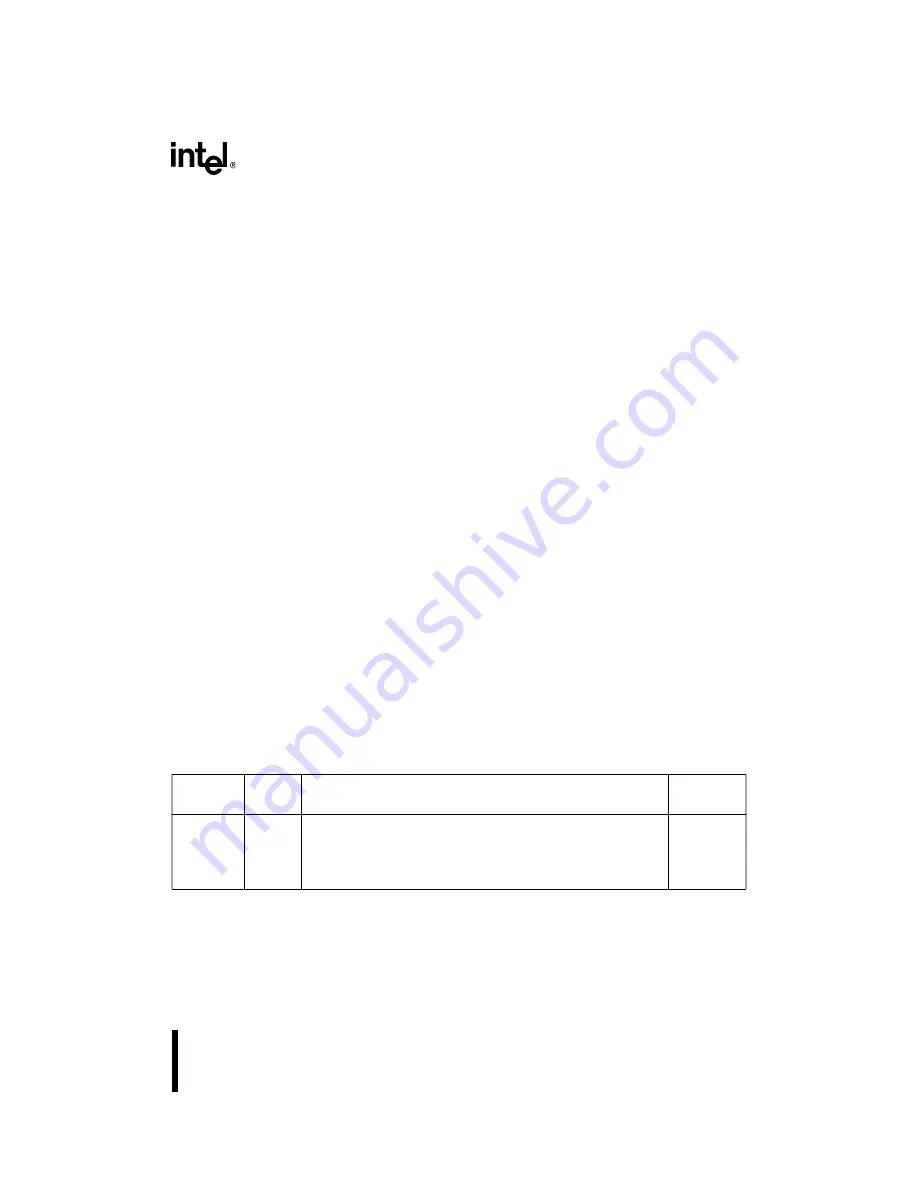

Table 6-1. Interrupt System Pin Signals

Signal

Name

Type

Description

Multiplexed

With

INT1:0#

I

External Interrupts 0 and 1. These inputs set bits IE1:0 in the

TCON register. If bits IT1:0 in the TCON register are set, bits IE1:0

are controlled by a negative-edge trigger on INT1#/INT0#. If bits

INT1:0# are clear, bits IE1:0 are controlled by a low level trigger on

INT1:0#.

P3.3:2

NOTE:

Other signals are defined in their respective chapters and in Appendix B, “Signal Descriptions.”

Summary of Contents for 8XC251SA

Page 2: ......

Page 3: ...May 1996 8XC251SA 8XC251SB 8XC251SP 8XC251SQ Embedded Microcontroller User s Manual...

Page 18: ......

Page 19: ...1 Guide to This Manual...

Page 20: ......

Page 30: ......

Page 31: ...2 Architectural Overview...

Page 32: ......

Page 41: ...3 Address Spaces...

Page 42: ......

Page 63: ...4 Device Configuration...

Page 64: ......

Page 81: ...5 Programming...

Page 82: ......

Page 102: ......

Page 103: ...6 Interrupt System...

Page 104: ......

Page 120: ......

Page 121: ...7 Input Output Ports...

Page 122: ......

Page 132: ......

Page 133: ...8 Timer Counters and Watchdog Timer...

Page 134: ......

Page 153: ...9 Programmable Counter Array...

Page 154: ......

Page 170: ......

Page 171: ...10 Serial I O Port...

Page 172: ......

Page 187: ...11 Minimum Hardware Setup...

Page 188: ......

Page 197: ...12 Special Operating Modes...

Page 198: ......

Page 206: ......

Page 207: ...13 External Memory Interface...

Page 208: ......

Page 239: ...14 Programming and Verifying Nonvolatile Memory...

Page 240: ......

Page 250: ......

Page 251: ...A Instruction Set Reference...

Page 252: ......

Page 390: ......

Page 391: ...B Signal Descriptions...

Page 392: ......

Page 400: ......

Page 401: ...C Registers...

Page 402: ......

Page 436: ......

Page 437: ...Glossary...

Page 438: ......

Page 446: ......

Page 447: ...Index...

Page 448: ......

Page 458: ......