82555 — Networking Silicon

50

Datasheet

11.4.8

10BASE-T Normal Link Pulse (NLP) Timing Parameters

11.4.9

Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters

T26a

T

R_CRSL

End of receive frame to falling

edge of CRS

10 Mbps

4.5

bits

T27

T

R_RXDVL

End of receive frame to falling

edge of RXDV

100 Mbps

12

bits

T27a

T

R_RXDVL

End of receive frame to falling

edge of RXDV

10 Mbps

4

bits

Symbol

Parameter

Conditions

Min

Typ

Max

Units

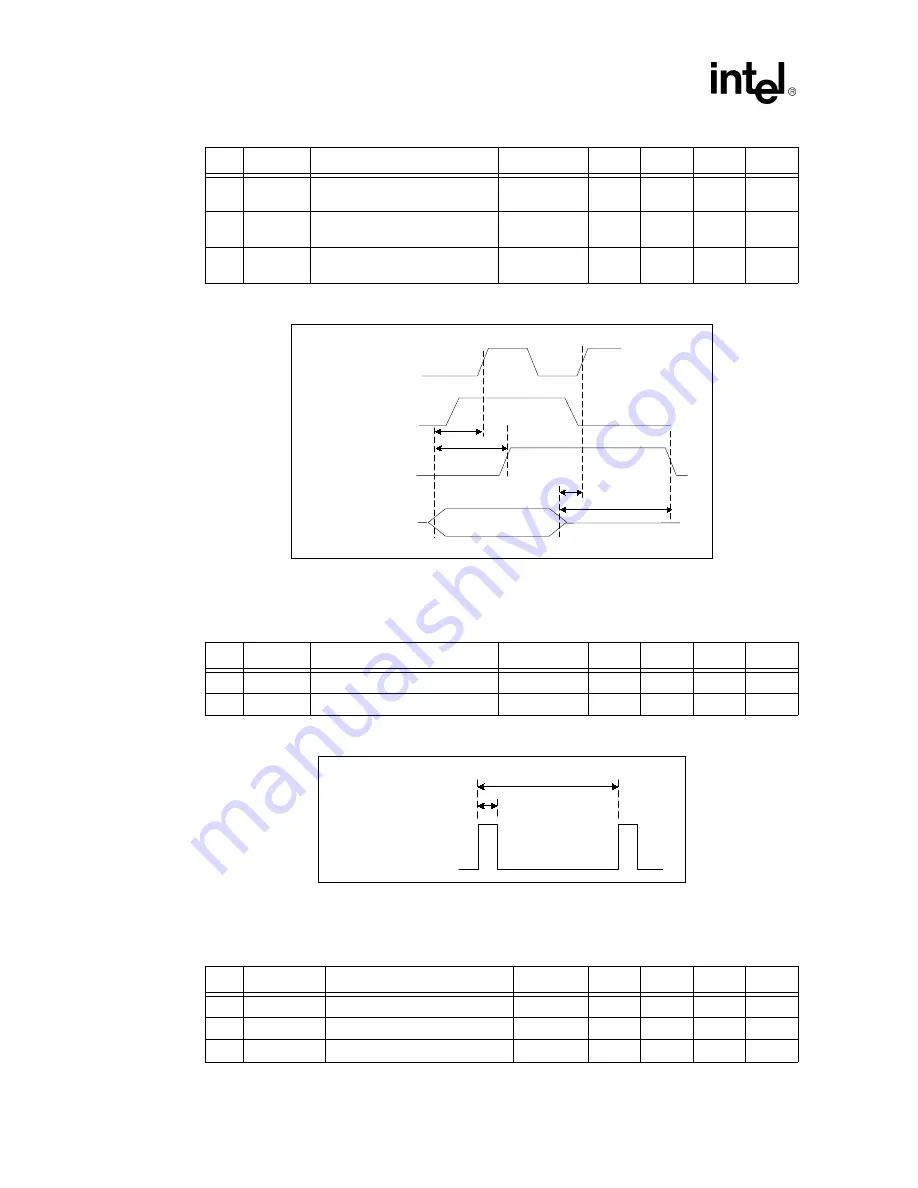

Figure 22. Receive Packet Timing Parameters

R X D V

C R S

Valid Frame Data

R X C L K

Frame On link

T25,T25a

T24,T24a

T26,T26a

T27,T27a

Symbol

Parameter

Conditions

Min

Typ

Max

Units

T28

T

NLP_WID

NLP width

10 Mbps

100

ns

T29

T

NLP_PER

NLP period

10 Mbps

8

24

ms

Figure 23. Normal Link Pulse Timing Parameters

N o r m a l L i n k P u l s e

T 2 9

T 2 8

Symbol

Parameter

Conditions

Min

Typ

Max

Units

T30

T

FLP_WID

FLP width (clock/data)

100

ns

T31

T

FLP_CLK_CLK

Clock pulse to clock pulse period

111

125

139

µ

s

T32

T

FLP_CLK_DAT

Clock pulse to data pulse period

55.5

62.5

69.5

µ

s