IDT Clocking, Reset, and Initialization

Clock Operation

PES24N3A User Manual

2 - 9

April 10, 2008

Notes

While slot power is enabled, the corresponding downstream port reset output is negated. When slot

power is disabled by writing a one to the PCC bit, the corresponding downstream port reset output is

asserted and then slot power is disabled. The time between the assertion of the PxRSTN signal and the

negation of the PxPEP signal is controlled by the value in the Reset Negation to Slot Power (RST2PWR)

field in the HPCFGCTL register.

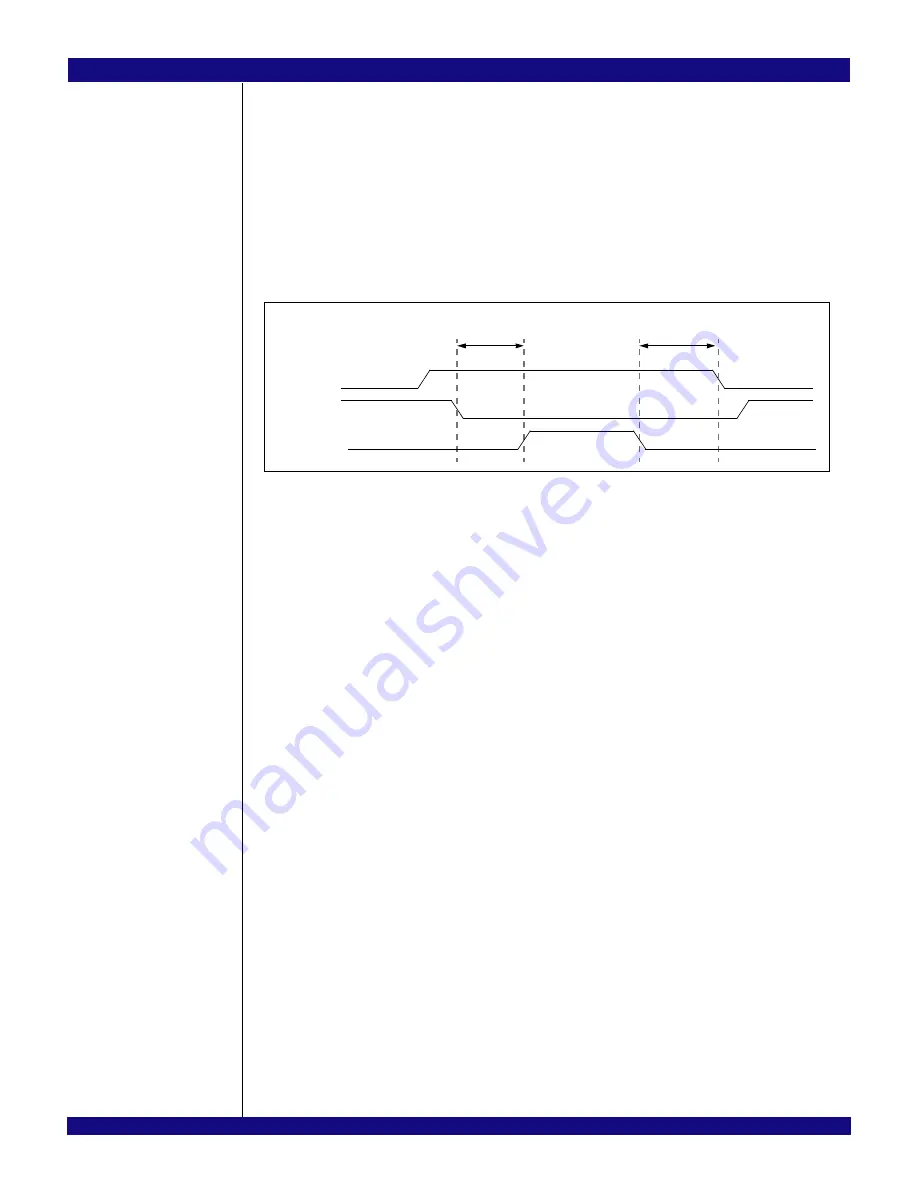

Power Good Controlled Reset Output

As in the Power Enable Controlled Reset mode, in this mode a downstream port reset output state is

controlled as a side effect of slot power being turned on or off. However, the timing in this mode depends on

the power good state of the slot’s power supply. The operation of this mode is illustrated in Figure 2.7.

Figure 2.7 Power Good Controlled Reset Output Mode Operation

The operation of this mode is similar to that of the Power Enable Controlled Reset mode except that

when power is enabled, the negation of the corresponding port reset output occurs as a result of and after

assertion of the slot’s Power Good (PxPWRGDN) signal is observed. The time between the assertion of the

PxPWRGDN signal and the negation of the PxRSTN signal is controlled by the value in the Slot Power to

Reset Negation (PWR2RST) field in the HPCFGCTL register.

When slot power is disabled by writing a one to the PCC bit, the corresponding downstream port reset

output is asserted and then slot power is disabled. The time between the assertion of the PxRSTN signal

and the negation of the PxPEP signal is controlled by the value in the Reset Negation to Slot Power

(RST2PWR) field in the HPCFGCTL register.

If at any point while a downstream port is not being reset (i.e., PxRSTN is negated) a power fault is

detected (i.e., PxPWRGDN is negated), the corresponding port reset output is immediately asserted. Since

the PxPWRGDN signal is an I/O expander input, it may not be possible to meet a profile’s power level

invalid to reset asserted timing specification (i.e., PxPWRGDN to PxRSTN). Systems that require a shorter

time interval may implement this functionality external to the PES24N3A.

Hot Reset Controlled Reset Output

In this mode the following conditions cause a downstream port’s reset output to be asserted:

–

Hot reset

–

Upstream secondary bus reset

–

Downstream secondary bus reset

When a downstream port reset output is asserted, it remains asserted while one of the above conditions

persists or for 200 µS, whichever is longer.

PxPEP

PxPWRGDN

T

PWR2RST

PxRSTN

T

RST2PWR

Summary of Contents for 89HPES24N3A

Page 10: ...IDT Table of Contents PES24N3A User Manual iv April 10 2008 Notes...

Page 12: ...IDT List of Tables PES24N3A User Manual vi April 10 2008 Notes...

Page 14: ...IDT List of Figures PES24N3A User Manual viii April 10 2008 Notes...

Page 18: ...IDT Register List PES24N3A User Manual xii April 10 2008 Notes...

Page 64: ...IDT Link Operation PES24N3A User Manual 4 8 April 10 2008 Notes...

Page 88: ...IDT Power Management PES24N3A User Manual 7 4 April 10 2008 Notes...

Page 160: ...IDT Configuration Registers PES24N3A User Manual 9 66 April 10 2008 Notes...