14. Register Descriptions > PCI Capability Registers

164

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

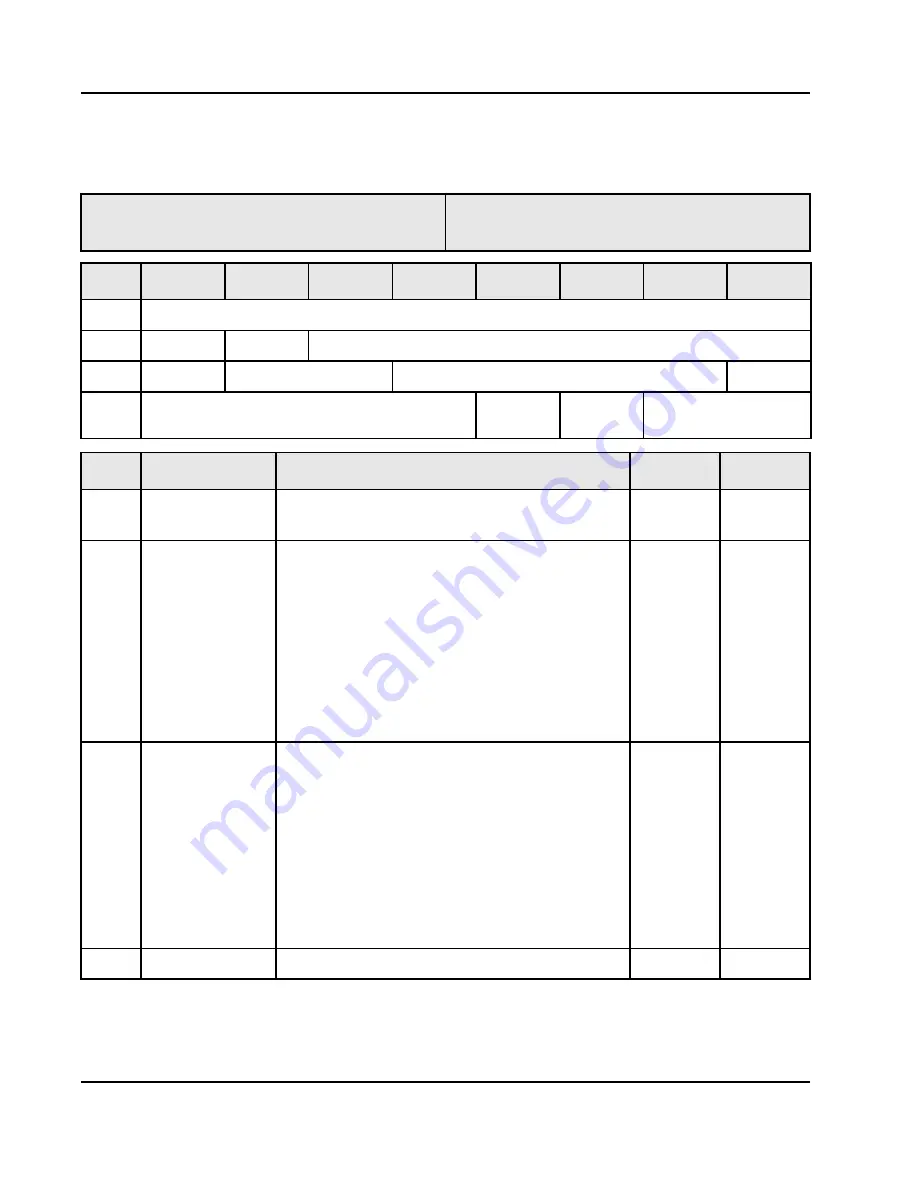

14.5.5

PCI Power Management Control and Status Register

This register defines the control and status registers of the power management capability option.

Register name: PCI_PMCS

Reset value: 0x0000_0008

Register offset: 0x0A4

Bits

7

6

5

4

3

2

1

0

31:24

DATA

23:16

BPCCE

B2B3S

Reserved

15:08

PME_ST

DATA_SC

DATA_SEL

PME_EN

07:00

Reserved

NO_SOFT_

RST

Reserved

PWR_ST

Bits

Name

Description

Type

Reset value

31:24

DATA

Power Data

The PEB383 does not support the Power Data field.

R

0x00

23

BPCCE

BPCC_En (Bus Power/Clock Control Enable) - A “1”

indicates that the bus power/clock control mechanism as

defined in Section 4.7.1 is enabled.

A “0” indicates that the bus power/clock control policies

defined in Section 4.7.1 have been disabled.

When the Bus Power/Clock Control mechanism is disabled,

the bridge’s PMCSR PowerState field cannot be used by the

system software to control the power or clock of the bridge’s

secondary bus.

This bit will be set if “PCGE” is set in

, and the PCI_CLK is 33MHz or less.

R

0x0

22

B2B3S

B2_B3# (B2/B3 support for D3hot) - The state of this bit

determines the action that is to occur as a direct result of

programming the function to D3hot.

A “1” indicates that when the bridge function is programmed

to D3hot, its secondary bus’s PCI clock will be stopped (B2).

A “0” indicates that when the bridge function is programmed

to D3hot, its secondary bus will have its power removed

(B3).

This bit is only meaningful if bit 7 (BPCC_En) is a “1”.

This bit will be set if “PCGE” is set in

, and the PCI_CLK is 33MHz or less.

R

0x0

21:16

Reserved

Reserved. It always reads 0.

R

0x0