USER GUIDE

REVISION C 09/29/14

1

©2014 Integrated Device Technology, Inc.

82P33731/33831 Evaluation Board

Introduction

The 82P33731/33831 evaluation board is designed to help the customer evaluate the IDT82P33731 and IDT82P33831 devices.

This user guide will accomplish the following:

•

Introduce the board on its power supply and jumper settings

•

Describe the input and output connectors for normal operation

•

How to bring up the board by using Timing Commander software GUI

•

How to configure and program the board to generate standard-compliant frequencies

Board Overview

Use

Figure 1

to identify various components of the board: Input and output SMA connectors; Power supply jacks and some

jumper settings necessary for the board operations. Detailed descriptions are as follows:

•

Input SMA Connectors –

There are a total of 14 inputs, of which IN1, 2 are AMI inputs; IN9, 10, 11, 12, 13, 14 are

single-ended inputs; IN3, 4, 5, 6, 7, 8 are differential inputs.

•

Output SMA Connectors

– There are a total of 12 outputs, of which OUT1, 2, 7, 9, 10 are single-ended outputs; OUT3, 4, 5,

6, 11, 12 are differential outputs; OUT8 is an AMI output.

•

USB connector –

Type-B connector for GUI communications. No power is drawn from USB connector other than to power

the FTDI USB chip.

•

Dip Switch SW6 –

Used to configure EEPROM write protection, master or slave selection and communication protocols

between PC/GUI and the board. For typical I

2

C mode, set MPU_MODE[1:0] = 00 ('I2C ON').

•

J76 –

This is a 2x12 pin header used to set communication mode between PC and the board.

Table 1

shows how to jump the

header pairs for the intended mode. Use JP18 (described below) to set I

2

C mode by default.

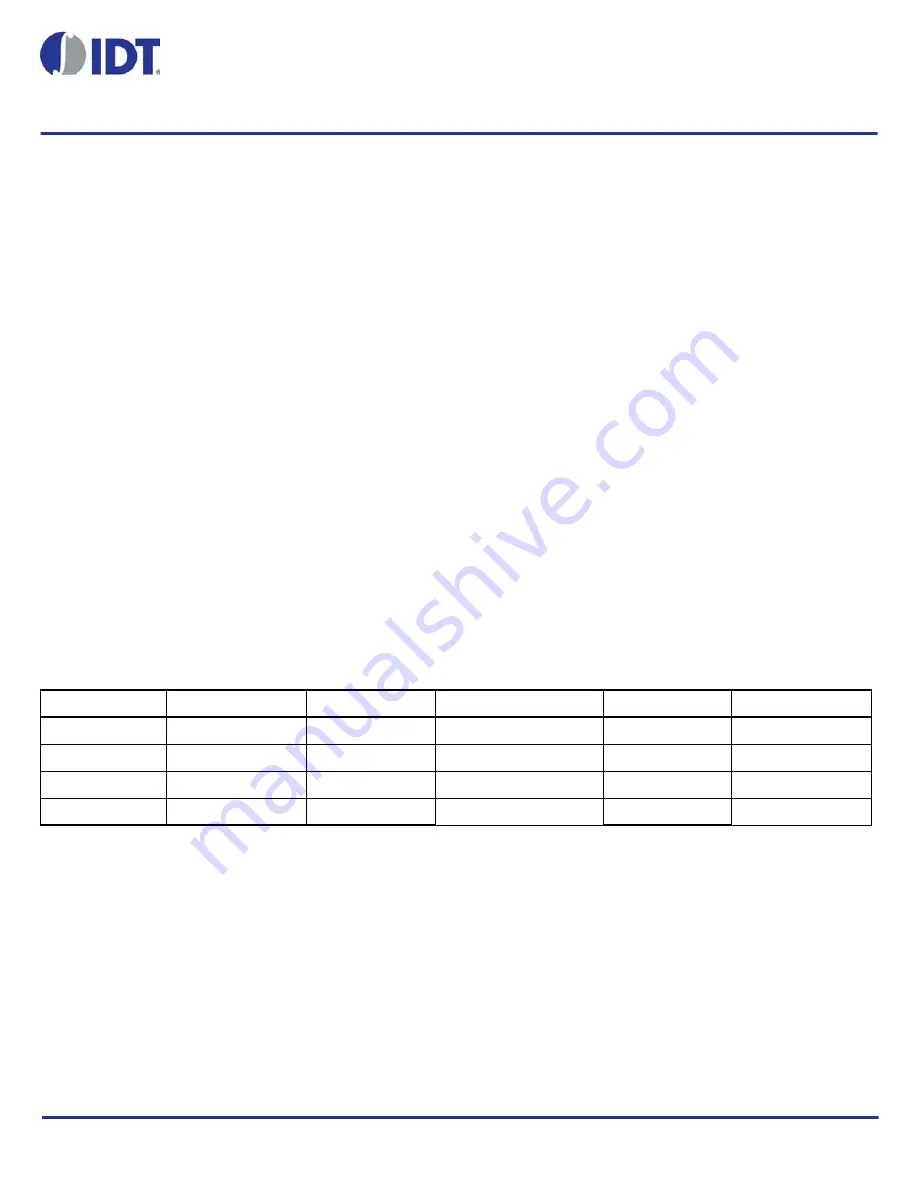

Table 1: Jumper Setting on J76

•

JP18

– By default, I

2

C mode will be selected with JP18 shunted (jumped).

FTDI SPI

Aardvark SPI/I2C

FTDI I2C

Motherboard SPI/I2C

FTDI UART

FTDI to Aardvark

3-4 Jumper

1-3 Jumper

3-4 Jumper

3-5 Jumper

4-6 Jumper

1-2 Jumper

9-10 Jumper

7-9 Jumper

9-10 Jumper

9-11 Jumper

9-10 Jumper

7-8 Jumper

15-16 Jumper

13-15 Jumper

14-16 Jumper

15-17 Jumper

15-16 Jumper

13-14 Jumper

21-22 Jumper

19-21 Jumper

21-23 Jumper

19-20 Jumper