12

IBM IntelliStation POWER 285 Technical Overview and Introduction

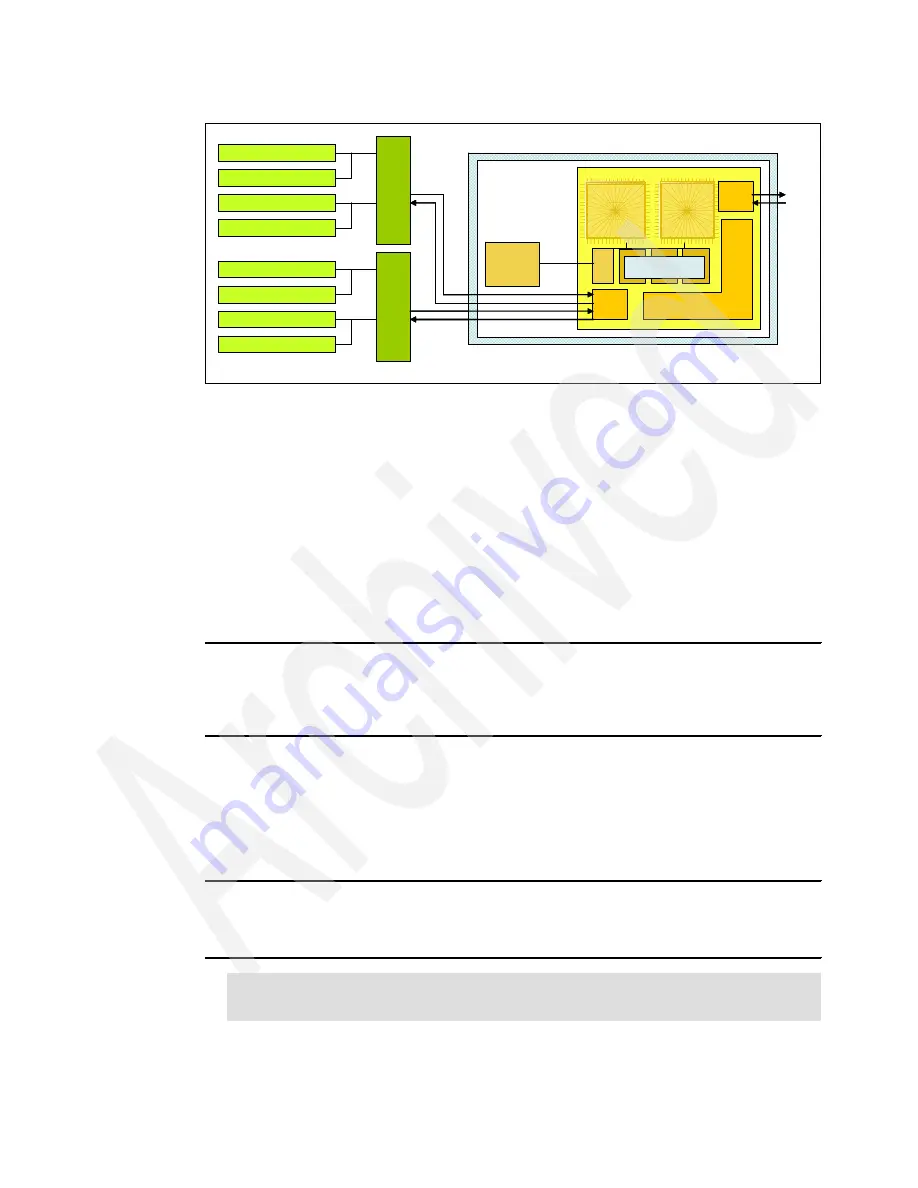

Figure 2-3 Two-core processor with DDR-2 memory socket layout view

Available processor speeds

The IntelliStation POWER 285 operates at a processor clock rate of 1.9 or 2.1 GHz for 1-core

and 2-core systems. To determine the processor characteristics on a running system, use

one of the following AIX 5L commands:

lsattr -El procX

Where

X

is the number of the processors, for example, proc0 is the first processor in the

system. The output from the command would be similar to the output in Example 2-1.

False

, as used in this output, signifies that the value cannot be changed through an AIX 5L

command interface.

Example 2-1 Output from lsattr -El procX command

type powerPC_POWER5

Processor type False

frequency 1896102000

Processor Speed False

smt_enabled true

Processor SMT enabled False

smt_threads 2

Processor SMT threads False

state enable

Processor state False

pmcycles -m

This command uses the performance monitor cycle counter and the processor real-time

clock to measure the actual processor clock speed in MHz. The output in Example 2-2 is

from a 2-core IntelliStation POWER 285 system running at 1.9 GHz with simultaneous

multithreading functionality enabled.

Example 2-2 Output from pmcycles -m command

Cpu 0 runs at 1896 MHz

Cpu 1 runs at 1896 MHz

Cpu 2 runs at 1896 MHz

Cpu 3 runs at 1896 MHz

Note: The

pmcycles

command is part of the bos.pmapi fileset. First check whether that

component is installed using the

lslpp -l bos.pmapi

command.

core

2.1 GHz

core

2.1 GHz

1.9 MB Shared

L2 cache

L3

Ctrl

Mem

Ctrl

36 MB

L3 cache

DCM

2x16B

@1.05 GHz

S

M

I-

II

S

M

I-

II

1056 MHz

2 x 8 B for read

2 x 2 B for write

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

2 x 8 B

@528 MHz

GX+

Ctrl

Enhanced distributed switch

GX+

Bus

core

2.1 GHz

core

2.1 GHz

core

2.1 GHz

core

2.1 GHz

1.9 MB Shared

L2 cache

L3

Ctrl

Mem

Ctrl

36 MB

L3 cache

DCM

2x16B

@1.05 GHz

S

M

I-

II

S

M

I-

II

1056 MHz

2 x 8 B for read

2 x 2 B for write

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

2 x 8 B

@528 MHz

GX+

Ctrl

Enhanced distributed switch

GX+

Bus