Travelstar 5K160 (PATA) Hard Disk Drive Specification

97

/

188

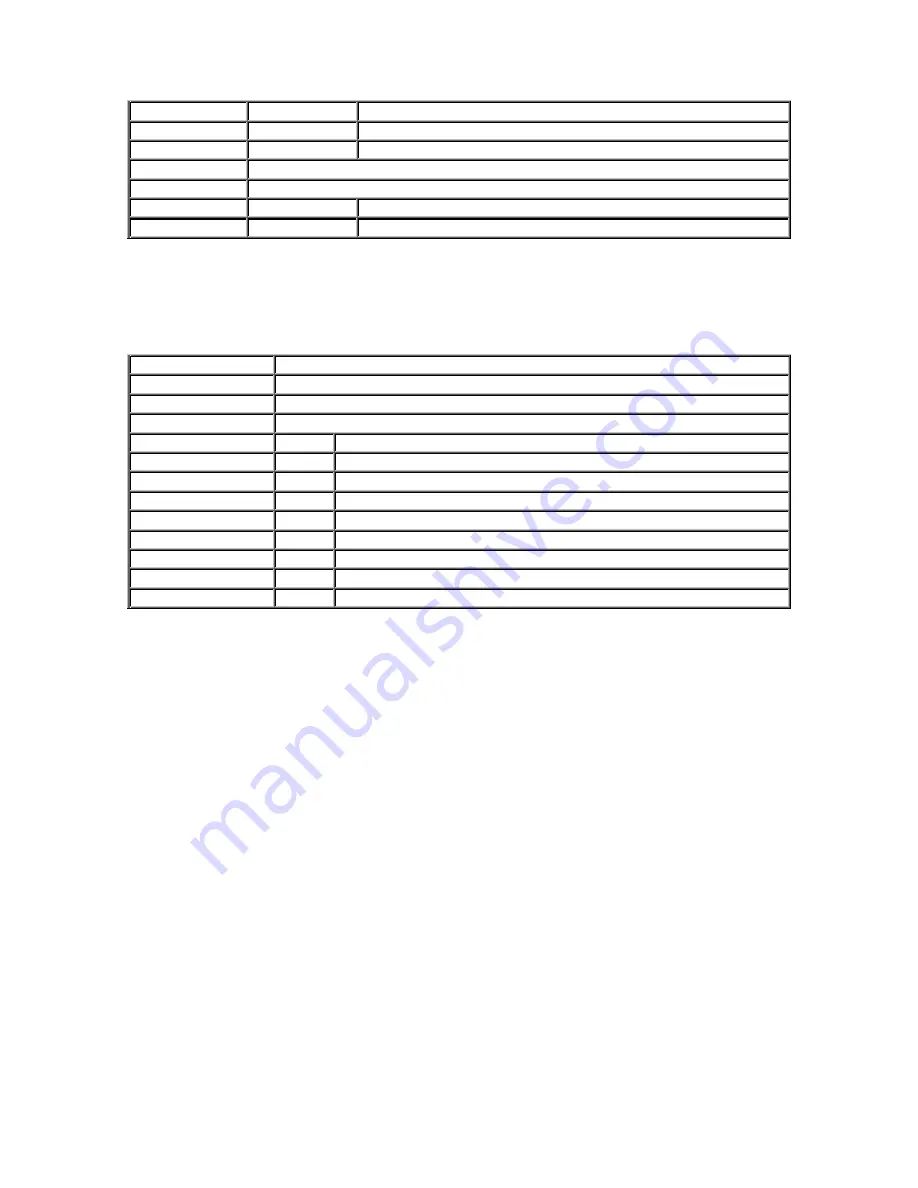

2 1 = SMART error log supported

1 1 = SMART self-test supported

0 1 = SMART feature set supported

8-254 Reserved

255

Integrity word <Note .>

15-8

Checksum

7-0

Signature (A5h)

Figure 44 Device Configuration Overlay Data structure

Note.

Bits 7:0 of this word contain the value A5h. Bits 15:8 of this word contain the data structure checksum. The data

structure checksum is the two's complement of the sum of all byte in words 0 through 254 and the byte consisting of

bits 7:0 of word 255. Each byte is added with unsigned arithmetic, and overflow is ignored. The sum of all bytes is

zero when the checksum is correct.

LBA High

invalid word location

LBA Mid

invalid bit location (bits (7:0))

LBA Low

invalid bit location (bits (15:8))

Sector count

error reason code & description

01h DCO feature is frozen

02h Device is now Security Locked mode

03h Device's feature is already modified with DCO

04h User attempt to disable any feature enabled

05h Device is now SET MAX Locked or Frozen mode

06h Protected area is now established

07h DCO is not supported

08h Subcommand code is invalid

FFh other reason

Figure 45 DCO error information definition