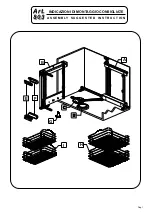

5K320 SATA OEM Specification

40

7.3

Signal definitions

The pin assignments of interface signals are listed as follows:

No.

Plug Connector pin definition

Signal

I/O

S1 GND

2nd

mate

Gnd

S2

A+

Differential signal A from Phy

RX+

Input

S3 A-

RX- Input

Signal S4 Gnd

2nd

mate

Gnd

S5

B-

Differential signal B from Phy

TX-

Output

S6 B+

TX+ Output

S7 Gnd

2nd

mate

Gnd

Key and spacing separate signal and power

segments

P1 V33

3.3V

power

3.3V

P2 V33

3.3V

power

3.3V

P3

V33

3.3V power, pre-charge, 2nd Mate

3.3V

P4 Gnd

1st

mate

Gnd

P5 Gnd

2nd

mate

Gnd

P6 Gnd

2nd

mate

Gnd

P7

V5

5V power,pre-charge,2nd Mate

5V

P8 V5

5V

power

5V

Power P9 V5

5V

power

5V

P10 Gnd

2nd

mate

Gnd

P11

DAS/DSS

Device Activity Signal / Disable

Staggered

Spinup

1

Note 1

P12 Gnd

1st

mate

Gnd

P13

V12

12V power,pre-chage,2nd mate

V12

P14 V12

12V

power

V12

P15 V12

12V

power

V12

Table 23. Interface connector pins and I/O signals

Note 1;

Pin P11 is used by the drive to provide the host with an activity indication and by the host to

indicate whether staggered spinup should be used.

The signal the drive provides for activity indication is a low-voltage low-current driver.

If pin P11 is asserted low the drive shall disable staggered spin-up and immediately initiate

spin-up. If pin P11 is not connected in the host (floating), the drive shall enable staggered spin-up.

7.3.1

TX+ / TX-

These signal are the outbound high-speed differential signals that are connected to the serial ATA

cable

7.3.2

RX+ / RX-

These signals are the inbound high-speed differential signals that are connected to the serial ATA

cable.

The following standard shall be referenced about signal specifications.

Serial ATA: High Speed Serialized AT Attachment Revision 1.0a 7-January -2003