- 26 -

➁

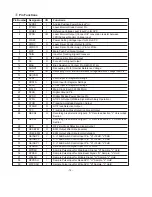

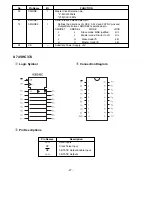

Pin Descriptions

No.

Pin Name

I/O

FUNCTION

1

AINR+

I

Right channel analog positive input pin

2

AINR-

I

Right channel analog negative input Pin

3

VREF

O

Voltage Reference output pin (VA-2.6V)

Normally connected to VA with a 0.luF ceramic capacitor in

parallel with a 10uF electrolytic capacitor.

4

VA

---

Analog section Analog Power Supply, +5V

5

AGND

---

Analog section Analog Ground

6

AINL+

I

Left channel analog positive input pin

7

AINL-

I

Left channel analog negative input pin

8

TST1

Test pin (Pull-down pin)

10

TST2

Should be left floating.

11

TST3

14

TST4

9

HPFE

I

High Pass Filter Enable pin(Pull-up pin)

"H": ON

"L": OFF

12

VD

---

Digital section Digital Power Supply pin, +5V

13

DGND

---

Digital section Digital Ground pin

16

PD

I

Power Down pin

"L" brings tne device into power-down mode. Must be done

once after power-on.

17

MCLK

I

Master Clock input pin

CMODE="H" : 384fs

CMODE="L" : 256fs

18

SCLK

I/O

Serial Data Clock pin

Data is clocked out at the falling edge of SCLK.

Slave mode: 64fs clock is input usually.

Master mode: SCLK outputs a 64fs clock.

SCLK stays low during the power-down mode(PD="L").

19

LRCK

I/O

L/R Channel Clock Select pin

Slave mode: An fs clock is fed to this LRCK pin.

Master mode: LRCK output an fs clock.

LRCK goes "H" at SMODE2="L" and "L" at SMODE2='"H"

during reset when SMODE1 "H".

20

FSYNC

I/O

Frame Synchronization Signal pin

Slave mode: When "H", data bits are clocked out on SDATA.

As I

2

S slave mode ignores FSYNC, it should hold "L" or "H".

Master mode: FSYNC outputs 2fs clock.

Stay low during the power-down mode(PD="L")

21

SDATA

O

Serial Data Output pin

Data are output with MSB first, in 2's complement format.

After 20 bits are output it turns to "L". It also remains "L"at a

power-down mode(PD="L").

Summary of Contents for CDR 2

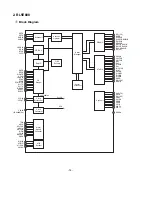

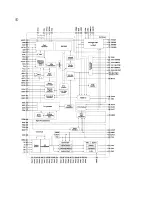

Page 13: ... 13 BLOCK DIAGRAM 1 AK8563 Block Diagram ...

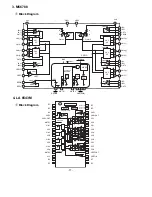

Page 18: ... 18 5 MN12511 Block Diagram D15 D0 NSDO VDD VSS VPP NCE NSCK NSDI CK CK OE OK R R OK ...

Page 19: ......

Page 20: ......

Page 21: ......

Page 22: ......

Page 23: ......

Page 24: ......

Page 25: ......

Page 29: ......

Page 30: ......

Page 31: ......

Page 32: ......

Page 33: ......

Page 34: ......

Page 35: ......

Page 36: ......

Page 37: ......

Page 38: ......

Page 39: ......

Page 40: ......

Page 41: ......

Page 42: ......

Page 43: ......

Page 44: ......

Page 45: ......

Page 46: ......

Page 47: ......

Page 48: ......

Page 49: ......

Page 50: ......

Page 51: ......

Page 52: ......

Page 53: ... 53 ...

Page 54: ... 54 ...

Page 55: ... 58 ASIC IC 301 74 105 107 BITSTR 1 IC 301 80 86 88 107 105 74 80 86 88 ...

Page 56: ... 59 U COM IC 202 12 14 16 12 14 16 ...

Page 60: ......

Page 61: ......

Page 62: ......

Page 63: ......

Page 64: ......

Page 65: ......

Page 66: ......

Page 67: ......

Page 68: ......

Page 69: ......

Page 70: ......

Page 71: ......

Page 72: ......

Page 73: ......

Page 74: ......

Page 75: ......

Page 76: ... 69 PCB LAYOUT CD PLAY TOP SECTION ...

Page 77: ... 70 CD PLAY BOTTOM SECTION ...

Page 78: ... 71 CD RECORD TOP SECTION CD RECORD BOTTOM SECTION ...

Page 79: ... 72 AUDIO TOP SECTION AUDIO BOTTOM SECTION ...

Page 80: ... 73 FRONT SECTION ...

Page 81: ... 74 POWER SECTION ...

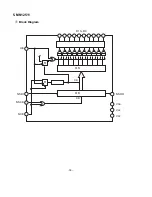

Page 82: ... 75 BLOCK DIAGRAM CD RECORD SECTION ...

Page 83: ... 76 CD PLAY SECTION ...

Page 85: ... 78 WIRING DIAGRAM ...