eRide

OPUS 6/

eRide

OPUS 7 GV-86/ GV-87

Dead Reckoning User

’

s Guide

SE16-900-002-00

6

FURUNO ELECTRIC CO., LTD. All rights reserved.

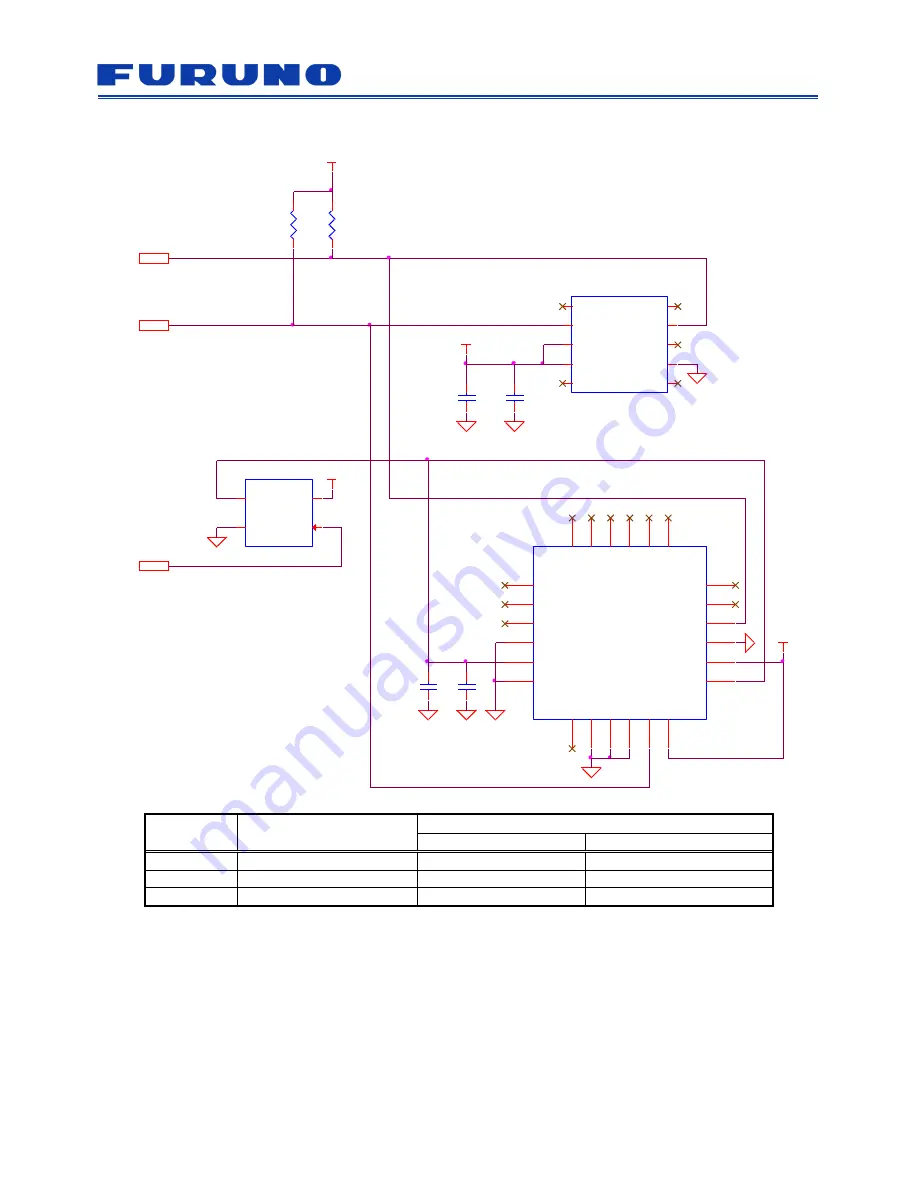

4.3 XV-4001BC and AIS328DQ

I/O signal

Description

Interface connection destination

eRideOPUS 6/7

GV-86/ 87

RESET

External reset signal

NRST

RST_N

SCL

I2C clock

TXD2_SCL

TXD2_SCL

SDA

I2C address/data bus

RXD2_SDA

RXD2_SDA

Figure 4.3 Reference Circuit of XV-4001BC and AIS328DQ

R1

10k

R2

10k

VCC

VCC

U2

XC8101AA01-GR-G

VOUT

1

VSS

2

CE

3

VIN

4

SDA

RESET

SCL

U3

AIS328DQ

NC

1

NC

2

INT_2

3

Reserv ed

4

VDD

5

GND

6

IN

T

_1

7

GN

D

8

GN

D

9

GN

D

10

SPC

/SC

L

11

CS

12

Reserv ed

13

VDD_IO

14

SDO/SA0

15

SDI/SDO/SDA

16

NC

17

NC

18

NC

19

NC

20

NC

21

NC

22

NC

23

NC

24

C3

10uF

C4

0.1uF

VCC

U1

XV-4001BC

Reserv ed

1

SCL

2

SS

3

VDD

4

Reserv ed

5

Reserv ed

6

GND

7

MOSI

8

SDA

9

Reserv ed

10

VCC

C2

10uF

C1

0.1uF

(*1)

(*1)

(*1)

(*4)

(*3)

(*3)

(*2)

(*2)

(*2)