MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

285

CHAPTER 16 LOW-VOLTAGE DETECTION RESET CIRCUIT

16.4 Operation

16.4

Operation

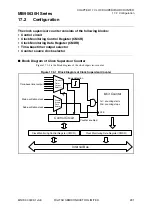

The low-voltage detection reset circuit generates a reset signal if the power

supply voltage falls below the detection voltage.

■

Reset Threshold Voltage

In the case of changing the reset threshold voltage in the LVDR register, the new threshold

voltage does not start to take effect until the LVD reset threshold voltage transition

stabilization time (t

stb

) elapses. For details of t

stb

, refer to the device data sheet.

■

Operation of Low-voltage Detection Reset Circuit

The low-voltage detection reset circuit generates a reset signal if the power supply voltage falls

below the low-voltage detection voltage. Afterward, if the low-voltage detection reset circuit

detects the low-voltage detection reset release voltage, it outputs a reset signal lasting for the

oscillation stabilization wait time and then releases the reset.

For details of the electrical characteristics, refer to the device data sheet.

Figure 16.4-1 Operation of Low-voltage Detection Reset Circuit

■

Operation in Standby Mode

The low-voltage detection reset circuit keeps operating even in standby mode (stop mode, sleep

mode, subclock mode and watch mode).

Vcc

Re

s

et

s

ign

a

l

A: Del

a

y

B: O

s

cill

a

tion

s

t

ab

iliz

a

tion w

a

it time

Oper

a

ting volt

a

ge

lower limit

Detection volt

a

ge/

re

s

et rele

as

e volt

a

ge

A

A

A

B

B

B