MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

239

CHAPTER 14 LIN-UART

14.6 Operations of LIN-UART and LIN-UART

Setting Procedure Example

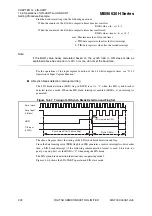

Figure 14.6-15 Master/Slave Mode Communication Flow Chart

NO

YE

S

YE

S

NO

NO

NO

YE

S

YE

S

YE

S

NO

S

t

a

rt

S

t

a

rt

(M

as

ter CPU)

(

S

l

a

ve CPU)

S

et to oper

a

ting mode 1

S

et to oper

a

ting mode 1

S

et

S

IN pin for

s

eri

a

l d

a

t

a

inp

u

t.

S

et

S

OT pin for

s

eri

a

l d

a

t

a

o

u

tp

u

t.

S

et

S

IN pin for

s

eri

a

l d

a

t

a

inp

u

t.

S

et

S

OT pin for

s

eri

a

l

d

a

t

a

o

u

tp

u

t.

S

et 7 or

8

d

a

t

a

b

it

s

.

S

et 1 or 2

s

top

b

it

s

.

S

et 7 or

8

d

a

t

a

b

it

s

.

S

et 1 or 2

s

top

b

it

s

.

S

et AD

b

it to "1"

En

ab

le tr

a

n

s

mi

ss

ion/

reception

En

ab

le tr

a

n

s

mi

ss

ion/

reception

Tr

a

n

s

mit

a

ddre

ss

to

s

l

a

ve

Receive

b

yte

s

AD

b

it = 1

S

et AD

b

it to "0"

Comm

u

nic

a

te with

s

l

a

ve

CPU

Termin

a

te

comm

u

nic

a

tion?

Comm

u

nic

a

te

with

a

nother

s

l

a

ve

CPU

Di

sab

le tr

a

n

s

mi

ss

ion/

reception

End

S

l

a

ve

a

ddre

ss

m

a

tche

s

a

ddre

ss

d

a

t

a

Comm

u

nic

a

te with m

as

ter

CPU

Termin

a

te

comm

u

nic

a

tion?