MB95630H Series

MN702-00009-2v0-E

FUJITSU SEMICONDUCTOR LIMITED

503

CHAPTER 24 I

2

C BUS INTERFACE

24.6 Operations and Setting Procedure Example

24.6.1

l

2

C Bus Interface

The I

2

C bus interface is an eight-bit serial interface synchronized with the shift

clock.

■

I

2

C System

The I

2

C bus system uses the serial data line (SDAn) and serial clock line (SCLn) for data

transfers. All the devices connected to the bus require open drain or open collector outputs

which must be connected with a pull-up resistor.

Each of the devices connected to the bus has a unique address which can be set up using

software. The devices always operate in a simple master/slave relationship, where the master

functions as the master transmitter or master receiver. The I

2

C bus interface is a true multi-

master bus with a collision detection function and arbitration function to prevent data from

being lost if more than one master attempts to start data transfer at the same time.

■

I

2

C Protocol

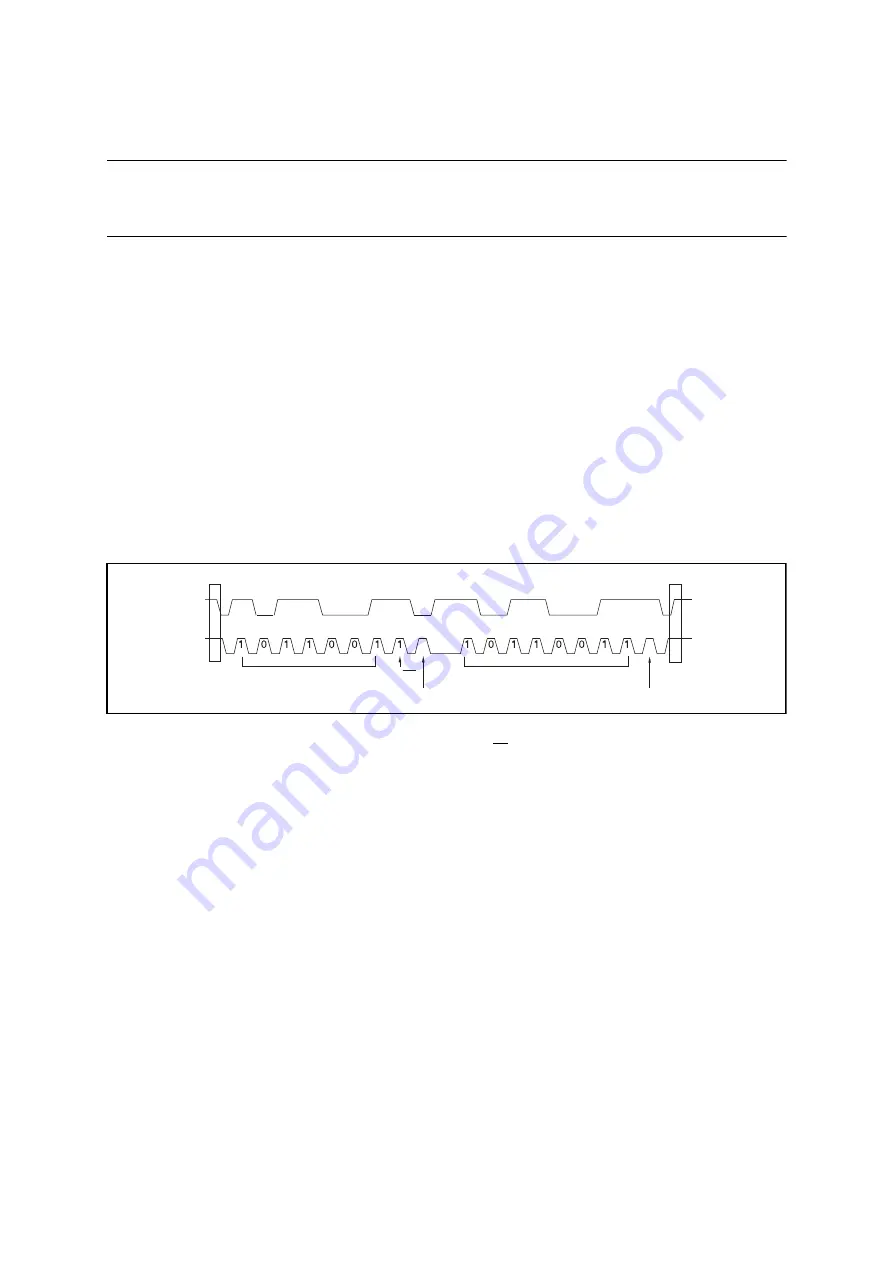

Figure 24.6-1 shows the format required for data transfer.

Figure 24.6-1 Data Transfer Example

The slave address is transmitted after a start condition (S) is generated. This address is seven

bits long followed by the data direction bit (R/W) in the eighth bit position. Data is transmitted

after the address. The data is eight bits followed by an acknowledgment.

Data can be transmitted continuously to the same slave address in consecutive units of eight

bits plus acknowledgment.

Data transfer is always ended in the master stop condition (P). However, the repeated start

condition (S) can be used to transmit the address which indicates a different slave without

generating a stop condition.

SDAn

SCLn

R/W

LSB

MSB

MSB

LSB

Start

condition (S)

7-bit address

Acknowledge bit

8-bit data

No acknowledge

Stop

condition (P)

Summary of Contents for 8FX

Page 2: ......

Page 4: ......

Page 8: ...iv ...

Page 18: ...xiv ...

Page 22: ...xviii ...

Page 650: ......