SIC63616-(Rev. 1.0) NO. P34

3240-0412

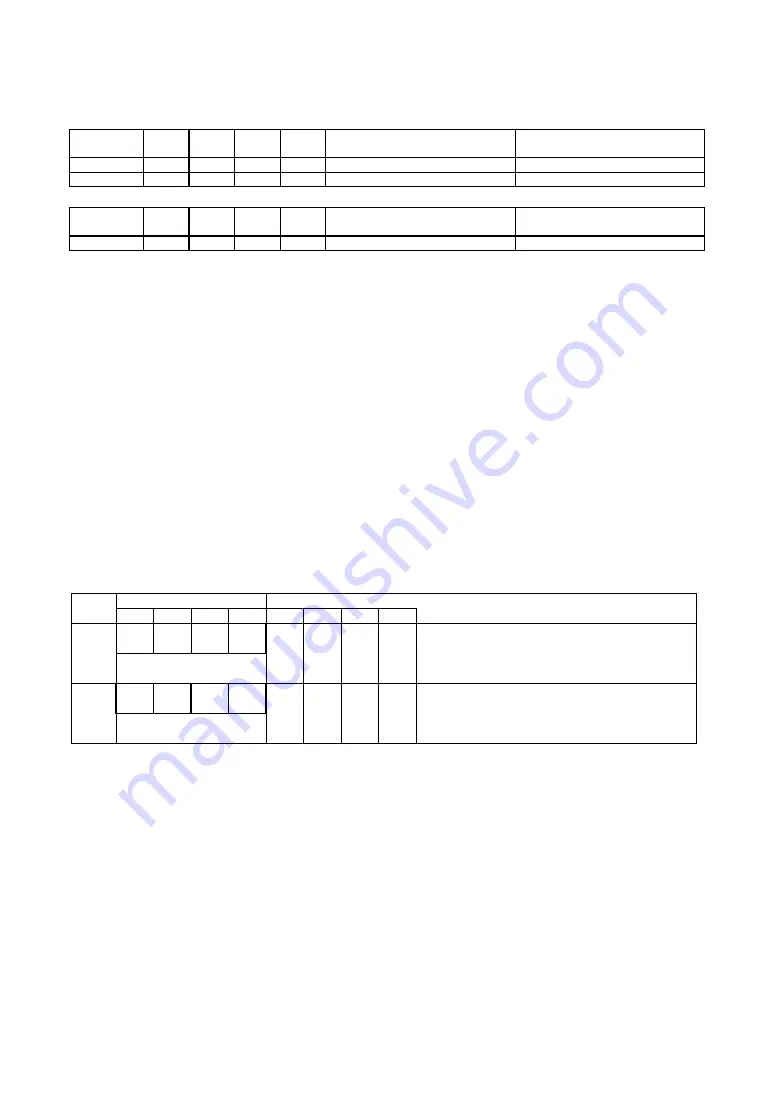

Table 4.2.2.1 lists settings of the above registers according to the supply voltage V

DD

.

Table 4.2.2.1 Power control register settings according to supply voltage V

DD

Power supply

voltage V

DD

1.6 to 2.5 V

2.5 to 5.5 V

DBON

1

0

HLON

0

0

VDSEL

0

0

VCSEL

1

0

Power source for internal and

oscillation system voltage regulators

V

DD

V

DD

Power source for LCD system

voltage regulator (V

C2

reference)

V

D2

(

≈

V

DD

×

2)

V

DD

When V

C2

reference LCD drive power option is selected

Power supply

voltage V

DD

1.6 to 5.5 V

DBON

0

HLON

0

VDSEL

0

VCSEL

0

Power source for internal and

oscillation system voltage regulators

V

DD

Power source for LCD system

voltage regulator (V

C1

reference)

V

DD

When V

C1

reference LCD drive power option is selected

4.2.3 Heavy load protection function

In order to ensure a stable circuit behavior and LCD display quality even if the power supply voltage

fluctuates due to driving an external load, the internal operating voltage regulator and the LCD system

voltage regulator have a heavy load protection function.

The internal operating voltage regulator enters heavy load protection mode by writing "1" to the

VDHLMOD register and it ensures stable V

D1

output. Use the heavy load protection function when a heavy

load such as a lamp or buzzer is driven with a port output.

The LCD system voltage regulator enters heavy load protection mode by writing "1" to the VCHLMOD

register and it ensures stable V

C1

–V

C5

outputs. Use the heavy load protection function when the LCD

display has inconsistencies in density.

Note: Current consumption increases in heavy load protection mode, therefore do not set heavy load

protection mode with software if unnecessary.

4.2.4 I/O memory for power control

Table 4.2.4.1 shows the I/O address and the control bits for power control.

Table 4.2.4.1 Power control bits

Address

Comment

D3

D2

Register

D1

D0

Name Init

∗

1

1

0

FF03H

VCHLMOD VDHLMOD General LPWR

R/W

VCHLMOD

VDHLMOD

General

LPWR

0

0

0

0

On

On

1

On

Off

Off

0

Off

Heavy load protection mode On/Off for LCD system voltage regulator

Heavy load protection mode On/Off for internal voltage regulator

General-purpose register

LCD system voltage regulator On/Off

FF02H

VDSEL VCSEL HLON

DBON

R/W

VDSEL

VCSEL

HLON

DBON

0

0

0

0

1

V

D2

On

On

0

V

DD

Off

Off

General-purpose register

Power source select for LCD system voltage regulator

Power voltage booster/halver halving mode On/Off

Power voltage booster/halver boost mode On/Off

*1 Initial value at initial reset

*3 Constantly "0" when being read

*2 Not set in the circuit

DBON: Power supply voltage booster/halver boost mode On/Off register (FF02H•D0)

Activates the power supply voltage booster/halver in boost mode.

When "1" is written: Booster On

When "0" is written: Booster Off

Reading: Valid

When "1" is written to DBON, the power supply voltage booster/halver activates in boost mode and almost

doubles the V

DD

voltage to generate the V

D2

voltage. Turn the power supply voltage booster/halver on

when driving the LCD system voltage regulator with V

D2

(V

C2

reference voltage, V

DD

= 1.6 to 2.5 V). When

"0" is written to DBON, the voltage boost operation is deactivated. Be sure to set DBON to "0" (Off) when

driving the LCD system voltage regulator with V

DD

. Furthermore, do not set both DBON and HLON to "1".

At initial reset, this register is set to "0".