- 45 -

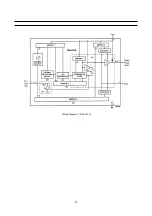

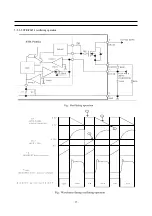

5-3-11 Video Sync Processing

To extract the sync information from the video signal, a linear phase low-pass filter eliminates all noise and video

contents above 1 MHz. The sync is separated by a slicer; the sync phase is measured. A variable window can be

selected to improve the noise immunity of the slicer. The phase comparator measures the falling edge of sync, as well

as the integrated sync pulse. The sync phase error is filtered by a phase-locked loop that is computed by the Fast

Processor. All timing in the front-end is derived from a counter that is part of this PLL, and it thus counts synchro-

nously to the video signal. A separate hardware block measures the signal back porch and also allows gathering the

maximum/minimum of the video signal. This information is processed by the FP and used for gain control and

clamping. For vertical sync separation, the sliced video signal is integrated. The FP uses the integrator value to derive

vertical sync and field information. The information extracted by the video sync processing is multiplexed onto the

hardware front sync signal (FSY) and is distributed to the rest of the video processing system.

The data for the vertical deflection, the sawtooth, and the East-West correction signal is calculated by the VCT 38xxA.

5-3-12 Display Processing

In the display processing the conversion from digital YC r C b to analogue RGB is carried out.

In the luminance processing path, contrast and brightness adjustments and a variety of features, such as black-level

expansion, dynamic peaking and soft limiting, are provided. In the chrominance path, the C r C b signals are converted

to 4:4:4 format and filtered by a colour transient improvement circuit. The YC r C b signals are converted by a program-

mable matrix to RGB colour space. The digital OSD insertion circuit allows the insertion of a 5-bit OSD signal.

The OSD signals and the display clock are synchronised to the horizontal flyback.

5-3-13 Chroma Transient Improvement

The intention of this block is to enhance the chroma resolution. A correction signal is calculated by differentiation of

the colour difference signals. The differentiation can be selected according to the signal bandwidth, e.g. for PAL/NTSC/

SECAM or digital component signals, respectively. The amplitude of the correction signal is adjustable. Small noise

amplitudes in the correction signal are suppressed by an adjustable coring circuit. To eliminate ‘wrong colours’, which

are caused by over and undershoots at the chroma transition, the sharpened chroma signals are limited to a proper value

automatically.

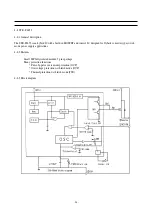

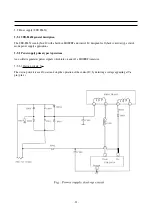

5-3-14 Video Back-end

The digital RGB signals are converted to analogue RGBs using three video digital-to-analogue converters (DAC) with

10-bit resolution. An analogue brightness value is provided by three additional DACs. The adjustment range is 40 % of

the full RGB range. Controlling the white-drive/analogue brightness and also the external contrast and brightness

adjustments is done via the Fast Processor, located in the front-end. Control of the cutoff DACs is done via I 2 C bus

registers. Finally cutoff and blanking values are added to the RGB signals. Cutoff (dark current) is provided by three 9-

bit DACs. The adjustment range is 60 % of full scale RGB range. The analogue RGB-outputs are current outputs with

current-sink characteristics. The maximum current drawn by the output stage is obtained with peak white RGB. An

external half contrast signal can be used to reduce the output current of the RGB outputs to 50% . Cutoff and white-

drive current measurement are carried out during the vertical blanking interval. They always use the small bandwidth

setting.

Summary of Contents for DTP-28B1

Page 29: ...29 Block diagram TDA8944J...

Page 32: ...32...

Page 34: ...34 Block diagram TDA6107Q...

Page 39: ...39 5 Circuit description 5 1 Block diagram...

Page 57: ...57 5 9 2 2 STR F6654 oscillating operation...

Page 73: ...73 7 Exploded View 7 5 DTP 28B1...

Page 74: ...PRINTED CIRCUIT BOARD PCB MAIN...

Page 75: ......

Page 76: ......