CMT2380F17

Rev0.1 | 158/347

www.cmostek.com

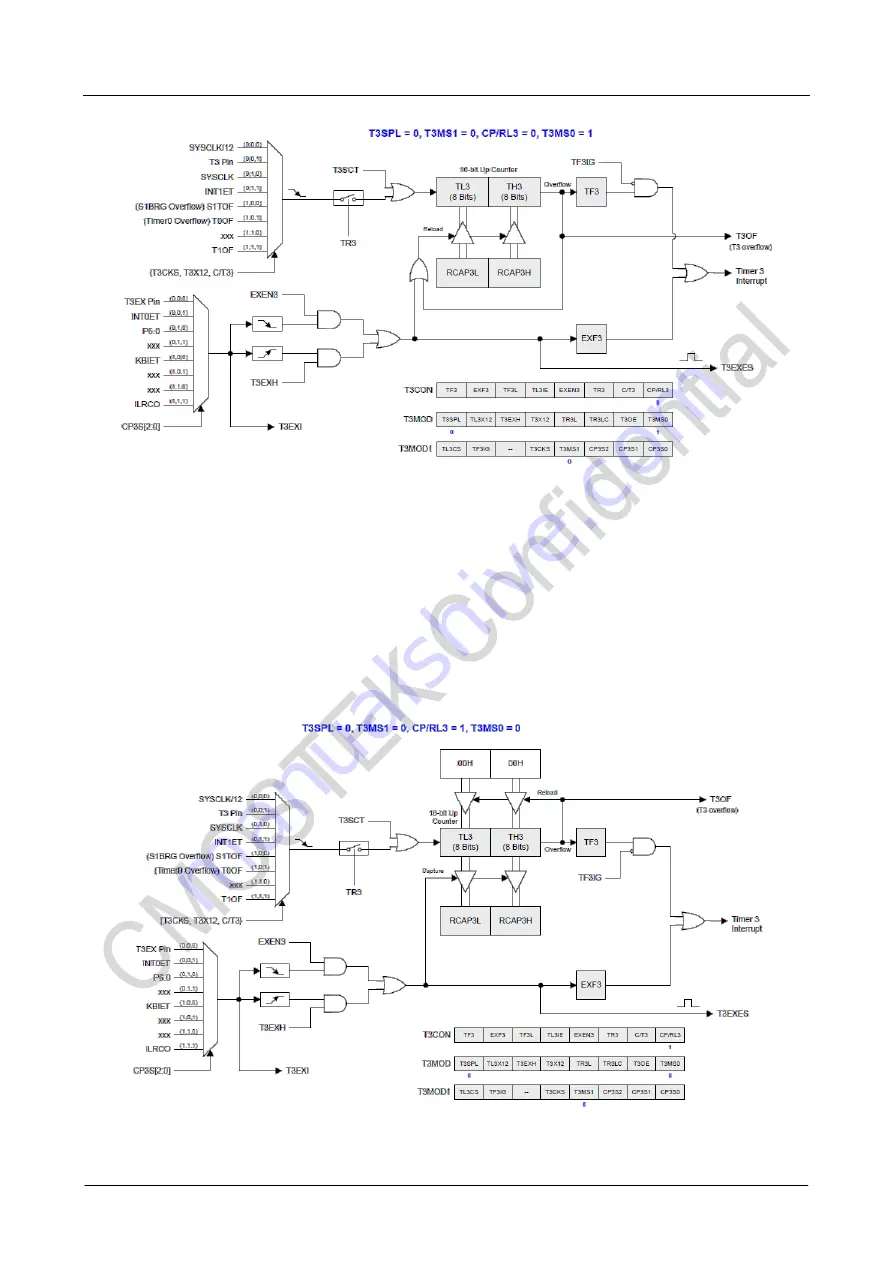

Figure 16-28. Timer 3 Mode 1 Structure (Auto-Reload with External Interrupt Mode)

16.3.3

Timer 3 Mode 2 (Capture)

Figure 16

–29 shows the capture mode there are two options selected by bit EXEN3 in T3CON. If

EXEN3=0, Timer 3 is a 16-bit timer or counter which, upon overflow, sets bit TF3 (Timer 3 overflow flag). This

bit can then be used to generate an interrupt (by enabling the Timer 3 interrupt bit in the EIE2 register). If

EXEN3=1, Timer 3 still does the above, but with the added feature that a 1-to-0 transition at T3EXI, one of 8

Timer 3 external inputs, that causes the current value in the Timer 3 registers, TH3 and TL3, to be captured

into registers RCAP3H and RCAP3L, respectively. In addition, the transition at T3EXI causes bit EXF3 in

T3CON to be set, and the EXF3 bit (like TF3) can generate an interrupt which vectors to the same location as

Timer 3 overflow interrupt. T3EXH performs the same function as EXEN3 but it enables the detecting a 0-to-1

transition at T3EXI input.

Figure 16-29. Timer 3 Mode 2 Structure (Capture Mode)

Summary of Contents for CMT2380F17

Page 27: ...CMT2380F17 Rev0 1 27 347 www cmostek com 1 25 Phase Noise...

Page 177: ...CMT2380F17 Rev0 1 177 347 www cmostek com Figure 17 3 PCA Interrupt System...

Page 246: ...CMT2380F17 Rev0 1 246 347 www cmostek com SnMIPS S0MI S1MI 1 P3 3 P4 7...