HY57V641620HG

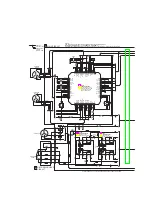

FUNCTIONAL BLOCK DIAGRAM

1Mbit x 4banks x 16 I/O Synchronous DRAM

X decoders

State Machine

A0

A1

A11

BA0

BA1

Address buffers

Address

Registers

Mode Registers

Row

Pre

Decoders

Column

Pre

Decoders

Column Add

Counter

Row active

Column

Active

Burst

Counter

Data Out Control

CAS Latency

Internal Row

counter

DQ0

DQ1

DQ14

DQ15

refresh

Self refresh logic

& timer

Pipe Line Control

I/O Buffer & Logic

Bank Select

Sense AMP & I/O Gate

CLK

CKE

CS

RAS

CAS

WE

UDQM

LDQM

1Mx16 Bank 3

X decoders

X decoders

Memory

Cell

Array

Y decoders

X decoders

1Mx16 Bank 0

1Mx16 Bank 1

1Mx16 Bank 2

18

Summary of Contents for DV523S

Page 1: ...SERVICE MANUAL DV523S...

Page 25: ...FRONT SCHEMATIC DIAGRAM 23...

Page 26: ...KEY2 Seg2 2 1 XS901 2P 2 0mm K901 STANDBY FRONT SCHEMATIC DIAGRAM 24...

Page 27: ...FRONT SCHEMATIC DIAGRAM 25...

Page 29: ...POWER BOARD SCHEMATIC DIAGRAM 27...

Page 31: ...OK SCHEMATIC DIAGRAM 29...

Page 33: ...OUTPUT BOARD 31...

Page 38: ...MIAN SCHEMATIC DIAGRAM 36...