writing to the data register at BASE+2 (Low nibble bits 0-3) and BASE + 3 (High byte bits 4-11). Prior

to this the DAC channel must be selected by writing a value of 02H to the Index register for DAC A

and 03H for DAC B.

Digital I/O

The APCI-ADADIO provides 16 digital I/O lines, these are grouped into four nibbles. Each nibble has

a power-up/reset state link and can be programmed as either input or output via the Digital I/O

configuration register.

Access to the individual I/O lines is via Index registers 0AH and 0BH. Reading these registers will

provide the status of all I/O lines regardless of whether they are configured as input or output. It is

possible to use these lines as bi-directional with some careful programming ensuring that a conflict

does not exist on any of these lines.

Note:

- If a nibble is to be used as an input the reset state link must be set to the high position,

otherwise the lines will be driven low as outputs which may cause damage.

Counter/Timer

The APCI-ADADIO contains an 8254 compatible counter/timer, which provides three 16-bit

counter/timers. Channel 0 can be used to trigger an A/D conversion and channel 1 can cause an

interrupt request sequence to be initiated.

A external connector (PL3) has been provided to allow internal or external signals to be used as clock

sources. The connector has been arranged to allow the on-board 1Mhz clock to be connected to the

clock input on channel 1 and 2 via links. The outputs of these timers can also be cascaded to provide

longer timing sequences.

Counter 0 should always be programmed in mode 2 which ensures that the output signal is only

active for a single clock cycle (i.e. 1uS when connected to the 1MHz clock). When the output from

counter 2 is used as the clock source the time between rising edges must not exceed 6 uS or be less

than 250nS.

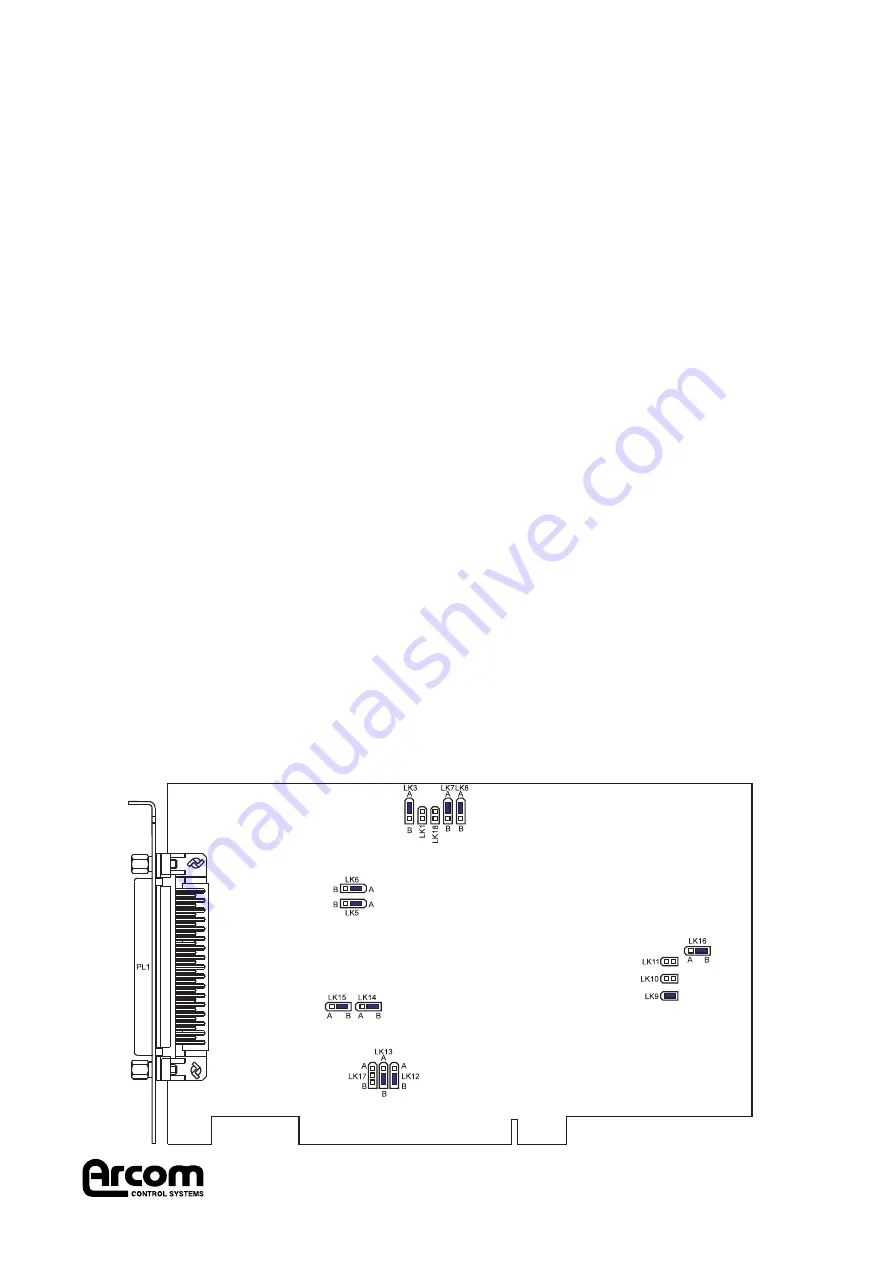

Links

Throughout this section a + indicates the default link position.

Default Link Position Diagram

Page 5

2192-09125-000-000

J605 APCI-ADADIO