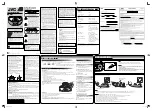

ISSUE

DRAWING NO.

DRAWING TITLE

DATE

Filename:

ECO No.

DESCRIPTION OF CHANGE

L974C2.sch

DV79 MAIN VADDIS V

Contact Engineer:

L974C2

23-Sep-2004

INITIALS

Printed:

2

11

Sheet

of

Notes:

Contact Tel:

(01223) 203270

Peter Gaggs

A & R Cambridge Ltd.

Pembroke Avenue

Cambridge CB5 9QR

Waterbeach

A1

ISSUE

DRAWING TITLE

DATE

Filename:

ECO No.

DESCRIPTION OF CHANGE

L974C2.sch

DV79 MAIN VADDIS V

Contact Engineer:

23-Sep-2004

INITIALS

Printed:

2

11

Sheet

of

Notes:

Contact Tel:

(01223) 203270

Peter Gaggs

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

RAMADD0

RAMADD1

RAMADD2

RAMADD3

RAMADD4

RAMADD5

RAMADD6

RAMADD7

RAMADD8

RAMADD9

RAMADD10

RAMBA0

RAMBA1

RAMADD0

RAMADD1

RAMADD2

RAMADD3

RAMADD4

RAMADD5

RAMADD6

RAMADD7

RAMADD8

RAMADD9

RAMADD10

RAMBA1

RAMBA0

DGND

+3V3D

+1V8D

DGND

+3V3D

VDDP_A

VDD_PLL

+3V3D

DGND

RAMDAT0

RAMDAT1

RAMDAT2

RAMDAT3

RAMDAT4

RAMDAT5

RAMDAT6

RAMDAT7

RAMDAT8

RAMDAT9

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMDAT16

RAMDAT17

RAMDAT18

RAMDAT19

RAMDAT20

RAMDAT21

RAMDAT22

RAMDAT23

RAMDAT24

RAMDAT25

RAMDAT26

RAMDAT27

RAMDAT28

RAMDAT29

RAMDAT30

RAMDAT31

RAMDAT31

RAMDAT0

RAMDAT1

RAMDAT2

RAMDAT3

RAMDAT4

RAMDAT5

RAMDAT6

RAMDAT7

RAMDAT8

RAMDAT9

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMDAT16

RAMDAT17

RAMDAT18

RAMDAT19

RAMDAT20

RAMDAT21

RAMDAT22

RAMDAT23

RAMDAT24

RAMDAT25

RAMDAT26

RAMDAT27

RAMDAT28

RAMDAT29

RAMDAT30

RAMDQM

RAMCS*

RAMRAS*

RAMCAS*

RAMWE*

RAMCKE

PCLK

RAMDQM

RAMCS*

RAMRAS*

RAMCAS*

RAMWE*

PCLK

RAMCKE

DGND

NF

NF

RAMADD7

RAMADD5

RAMADD6

RAMADD1

RAMADD0

RAMADD8

RAMADD10

RAMADD9

RAMDAT27

RAMDAT20

RAMDAT5

RAMDAT21

RAMDAT26

RAMDAT9

RAMDAT6

RAMDAT24

RAMBA1

RAMBA0

RAMADD11

RAMDAT8

RAMDAT7

RAMDAT22

RAMDAT25

RAMDAT23

RAMDAT18

RAMDAT31

RAMDAT30

RAMDAT16

RAMDAT17

RAMDAT29

RAMDAT28

RAMDAT19

RAMADD11

FRAMADD7

FRAMADD5

FRAMADD6

FRAMADD1

FRAMADD0

FRAMADD8

FRAMADD10

FRAMADD9

FRAMDAT27

FRAMDAT20

FRAMDAT5

FRAMDAT21

FRAMDAT26

FRAMDAT9

FRAMDAT6

FRAMDAT24

FRAMBA1

FRAMBA0

FRAMADD11

FRAMDAT8

FRAMDAT7

FRAMDAT22

FRAMDAT25

FRAMDAT23

FRAMDAT18

FRAMDAT31

FRAMDAT30

FRAMDAT16

FRAMDAT17

FRAMDAT29

FRAMDAT28

FRAMDAT19

+3V3D

DGND

FRAMADD5

FRAMADD6

FRAMADD7

FRAMADD8

FRAMADD9

FRAMADD11

FRAMDAT8

FRAMDAT9

FRAMDAT5

FRAMDAT6

FRAMDAT7

FRAMBA0

FRAMBA1

FRAMADD10

FRAMADD0

FRAMADD1

RAMADD2

FRAMADD2

FRAMADD2

RAMDAT10

FRAMDAT10

FRAMDAT10

RAMDAT11

FRAMDAT11

FRAMDAT11

RAMDAT4

RAMDAT3

RAMDAT12

NF (Intel 64Mb)

PWR_ON_RESET*

FLASHA19

FLASHA19

FRAMDAT3

FRAMDAT3

FLASHA21

FLASHA21

Use these resistors to configure for

Intel/AMD 8Mbit, 16Mbit, 32Mbit or

64Mbit devices

Intel 32Mbit is used for DV79

RAMADD4

FRAMADD4

FRAMADD4

+3V3D

PNVMCE*

PNVMCE*

RAMADD3

FRAMADD3

FRAMADD3

FRAMDAT31

FRAMDAT29

FRAMDAT27

FRAMDAT25

FRAMDAT23

FRAMDAT21

FRAMDAT19

FRAMDAT17

FRAMDAT30

FRAMDAT28

FRAMDAT26

FRAMDAT24

FRAMDAT22

FRAMDAT20

FRAMDAT18

FRAMDAT16

SDRAM

FLASH

ZORAN VADDIS V

+3V3D

DGND

+1V8D

DGND

VADDIS DECOUPLING

+3V3D

DGND

SDRAM DECOUPLING

+3V3D

DGND

FLASH DECOUPLING

ATDD0

ATDD1

ATDD2

ATDD3

ATDD4

ATDD5

ATDD6

ATDD7

ATDD8

ATDD9

ATDD10

ATDD11

ATDD12

ATDD13

ATDD14

ATDD15

ATDMARQ

ATDIOW*

ATDIOR*

ATIORDY

ATDMACK*

ATINTRQ

ATDA0

ATDA1

ATDA2

ATCS0*

ATCS1*

Audio master clock (input)

Can be configured as an output for testing

AMCLK_OUT

AMCLK_OUT

PWR_ON_RESET*

DGND

+3V3D

To enable Vaddis PLL for testing:

Make PLLCFGA low

Isolate AMCLK from GCLKA

Link GCLKA to GCLKP

Connect AMCLK_OUT to AMCLK

AMCLK is now an output and the Vaddis PLL is

enabled

Fit Link to boot from DEBUG UART

MUTE*

MUTE*

ML_8740_0

MC

MD

ML_8740_2

FSEL0

ML_8740_1

ML_8740_1

ML_8740_0

MC

MD

ML_8740_2

FSEL0

ENABLE_AV

16/9

GAIN_SCALING

ENABLE_AV

16/9

GAIN_SCALING

BOOT SELECT

+3V3D

Not Fitted

+3V3D

DGND

EJTAG DEBUG

EEPROM MEMORY

SERIAL_RX

SERIAL_TX

SDA

SCL

EJTRST

EJTDI

EJTDO

EJTMS

EJTCK

SERIAL PORT

IRRCV

IRRCV

SPDIF

ADAT1

ADAT2

ADAT0

ABCLK

ALRCLK

ALRCLK

ABCLK

ADAT0

ADAT2

ADAT1

SPDIF

DIGITAL AUDIO

CLOCKS

PSUFS0

PSUFS1

ATRESET*

XATRESET*

ATE can use test pad to put in debug boot mode

DGND

DGND

DGND

DGND

DGND

address

data

address

data

+3V3D

DGND

Decoupling caps on bottom of board

+1V8D

DGND

Decoupling caps on bottom of board

L200

120R@100MHz

L201

120R@100MHz

+3V3D

+1V8D

C248

10UF

50V

YK

C208

100N

16V

0603

DGND

C250

10UF

50V

YK

C210

100N

16V

0603

6

3

RP214C

100R

1

8

RP214A

100R

2

7

RP214B

100R

A0 1

A1 2

A2 3

SDA

5 SCL

6

WP

7

IC204A

24LC08BT/SN

SO-8

DGND

DGND

+3V3D

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

CON201

HARWIN

M20-972

1

8

RP215A

4K7

62mW

1206

2

7

RP215B

4K7

62mW

1206

6

3

RP215C

4K7

62mW

1206

5

4

RP215D

4K7

62mW

1206

NF

NF

TR200

MMUN2211LT1

SOT-23

1

2

CON200

HARWIN

M20-973

NF

CLK27M_VADDIS

MCLK_VADDIS

NF

C223

100N

16V

0603

C240

100N

16V

0603

C239

100N

16V

0603

C238

100N

16V

0603

C237

100N

16V

0603

C236

100N

16V

0603

C235

100N

16V

0603

C234

100N

16V

0603

C233

100N

16V

0603

C232

100N

16V

0603

C231

100N

16V

0603

C229

100N

16V

0603

C227

100N

16V

0603

C225

100N

16V

0603

C221

100N

16V

0603

C222

100N

16V

0603

C224

100N

16V

0603

C226

100N

16V

0603

C228

100N

16V

0603

C230

100N

16V

0603

V

D

D

1

DQ0 2

V

D

D

Q

3

DQ1 4

DQ2 5

V

SS

Q

6

DQ3 7

DQ4 8

V

D

D

Q

9

DQ5 10

DQ6 11

V

SS

Q

12

DQ7 13

V

D

D

15

DQM0

16

WE

17

CAS

18

RAS

19

CS

20

BA0

22

BA1

23

A10/AP

24

A0

25 A1

26 A2

27

DQM2

28

V

D

D

29

DQ16 31

V

SS

Q

32

DQ17 33

DQ18 34

V

D

D

Q

35

DQ19 36

DQ20 37

V

SS

Q

38

DQ21 39

DQ22 40

V

D

D

Q

41

DQ23 42

V

D

D

43

V

SS

44

DQ24 45

V

SS

Q

46

DQ25 47

DQ26 48

V

D

D

Q

49

DQ27 50

DQ28 51

V

SS

Q

52

DQ29 53

DQ30 54

V

D

D

Q

55

DQ31 56

V

SS

58

DQM3

59

A3

60 A4

61 A5

62 A6

63 A7

64 A8

65 A9

66

CKE

67

CLK

68

DQM1

71

V

SS

72

DQ8 74

V

D

D

Q

75

DQ9 76

DQ10 77

V

SS

Q

78

DQ11 79

DQ12 80

V

D

D

Q

81

DQ13 82

DQ14 83

V

SS

Q

84

DQ15 85

V

SS

86

A11 (NC)

21

IC203

IC MEM SDRAM 512KX32BITX4 7NS

C217

100N

16V

0603

R225

1K0

0W063

0603

C212

100N

16V

0603

C213

100N

16V

0603

C214

100N

16V

0603

C215

100N

16V

0603

C220

100N

16V

0603

1

8

RP200A

56R

2

7

RP200B

56R

6

3

RP200C

56R

5

4

RP200D

56R

1

8

RP201A

56R

2

7

RP201B

56R

6

3

RP201C

56R

5

4

RP201D

56R

1

8

RP202A

56R

2

7

RP202B

56R

6

3

RP202C

56R

5

4

RP202D

56R

1

8

RP203A

56R

2

7

RP203B

56R

6

3

RP203C

56R

5

4

RP203D

56R

1

8

RP204A

56R

2

7

RP204B

56R

6

3

RP204C

56R

5

4

RP204D

56R

1

8

RP205A

56R

2

7

RP205B

56R

6

3

RP205C

56R

5

4

RP205D

56R

1

8

RP206A

56R

2

7

RP206B

56R

6

3

RP206C

56R

5

4

RP206D

56R

1

8

RP207A

56R

2

7

RP207B

56R

6

3

RP207C

56R

5

4

RP207D

56R

1

8

RP208A

56R

2

7

RP208B

56R

6

3

RP208C

56R

5

4

RP208D

56R

GND 7

VCC 14

IC200E

74HCT125D

SO-14

C219

100N

16V

0603

+5VD

DGND

GND 4

VCC 8

IC204B

24LC08BT/SN

SO-8

C218

100N

16V

0603

+3V3D

DGND

V

C

C

RST

G

N

D

IC201

LM809M3-2.63

SOT-23

C207

100N

16V

0603

+3V3D

DGND

RESET*

PWR_ON_RESET*

RESET

CLK27M_VADDIS

MCLK_VADDIS

5

4

RP209D

33R

6

3

RP209C

33R

2

7

RP209B

33R

1

8

RP209A

33R

5

4

RP210D

33R

6

3

RP210C

33R

2

7

RP210B

33R

1

8

RP210A

33R

1

8

RP211A

33R

2

7

RP211B

33R

6

3

RP211C

33R

5

4

RP211D

33R

1

8

RP212A

33R

2

7

RP212B

33R

6

3

RP212C

33R

5

4

RP212D

33R

DGND

+5VD

ATRESET*

+5VD

DGND

Design note: Some Vaddis GPIO

initialise as o/p high, some as o/p

low.

MUTE must use one that initialises

as o/p low. Currently on pin T2

PSUFS0

PSUFS1

FPDOUT

FRONT PANEL

2

3

1

IC200A 74HCT125D

SO-14

5

6

4

IC200B 74HCT125D

SO-14

9

8

10

IC200C 74HCT125D

SO-14

DGND

DGND

DGND

DGND

FPDIN

FPCLK

FPSEL

12

11

13

IC200D

74HCT125D

SO-14

DGND

C200

47P

100V

0805

C205

47P

100V

0805

R206

56R

0W125 0805

R207

56R

0W125

0805

R208

56R

0W125

0805

R209

56R

0W125

0805

R210

56R

0W125

0805

R222

0R0

0W125

0805

R223

0R0

0W125

0805

R219

0R0

0W125

0805

R224

0R0

0W125

0805

R250

5K6

0W125

0805

R226

1K0

0W125

0805

R227

1K0

0W125

0805

R228

1K0

0W125

0805

R234

4K7

0W125

0805

R232

4K7

0W125

0805

R233

4K7

0W125

0805

R237

4K7

0W125

0805

R204

10K

0W125

0805

R251

33R

0W125

0805

R235

4K7

0W125

0805

R236

4K7

0W125

0805

R231

1K0

0W125

0805

R230

1K0

0W125

0805

R229

1K0

0W125

0805

R220

0R0

0W125

0805

R221

0R0

0W125

0805

FSEL1

DGND

DGND

PNVMR/B*

R252

56R

0W125

0805

PNVMR/B*

NF(AMD)

R253

56R

0W125

0805

RAMDAT4

NF(AMD 16Mb)

HS202

3319B+T410-01

20.9C/W

P242

R218

100R

0W125 0805

R254

100R

0W125 0805

R255

100R

0W125 0805

C253

100UF

10V

YXF

C252

100UF

10V

YXF

C254

100UF

10V

YXF

NF

R249

33R 0805

R248

33R 0805

R247

33R 0805

R246

33R 0805

R245

33R 0805

R244

33R 0805

R240

82R 0805

R243

22R 0805

R239

82R 0805

R242

22R 0805

R241

22R 0805

R238

82R 0805

+3V3D

P243

P244

P245

P246

P247

P248

P249

P250

P251

P252

P253

P254

P255

P256

P257

P258

P259

P260

P261

P262

P263

P264

P265

P266

P267

P268

P269

P270

PR220

PR221

PR222

PR223

PR224

PR225

PR226

PR227

PR228

PR229

PR230

PR231

PR232

PR233

PR234

PR235

PR236

PR237

PR238

PR239

PR240

PR241

PR242

PR243

PR244

PR245

PR246

PR247

PR248

PR249

PR250

PR251

PR200

PR201

PR202

PR203

PR204

PR205

PR206

PR207

PR208

PR209

PR210

PR211

PR212

PR213

PR214

PR215

PR216

PR217

PR218

PR219

PF224

PF225

PF226

PF227

PF239

PF240

PF241

PF242

PF216

PF217

PF218

PF219

PF220

PF221

PF222

PF223

PF200

PF201

PF202

PF203

PF204

PF205

PF206

PF207

PF208

PF209

PF210

PF211

PF212

PF213

PF214

PF215

PF228

PF229

PF230

PF231

PF232

PF233

PF234

PF235

PF236

PF237

PF238

P271

P273

PF243

PR252

P275

P274

P277

P276

P279

P278

P282

P201

P284

P285

P286

NOTE: JTAG port is for software debug only.

Boundary scan is not supported

P287

P288

P289

P290

P291

P292

P293

P294

P295

P296

PJ203

PJ205

PJ200

PR253

P200

P204

P203

P202

C245

1N0

50V

0603

C241

1N0

50V

0603

C243

1N0

50V

0603

C246

1N0

50V

0603

C247

1N0

50V

0603

C242

1N0

50V

0603

C244

1N0

50V

0603

+3V3D

CLK_27M_VID

VSYNC*

HSYNC*

VIDP[0..19]

VIDP[0..19]

VIDP0

VIDP1

VIDP2

VIDP3

VIDP4

VIDP5

VIDP6

VIDP7

VIDP8

VIDP9

VIDP10

VIDP11

VIDP12

VIDP13

VIDP14

VIDP15

VIDP16

VIDP17

VIDP18

VIDP19

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

CON203

Dubilier

C3

XATRESET*

DGND

ATDD7

ATDD8

ATDD6

ATDD9

ATDD5

ATDD10

ATDD4

ATDD11

ATDD3

ATDD12

ATDD2

ATDD13

ATDD1

ATDD14

ATDD0

ATDD15

ATDMARQ

ATDIOW*

ATDIOR*

ATIORDY

ATDMACK*

ATINTRQ

ATDA1

ATDA0

ATDA2

ATCS0*

ATCS1*

DRIVE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

CON202

MOLEX

52806

DGND

FPDOUT

XFPCLK

XFPSEL

XFPDIN

IRRCV

REM_BUS_P

FPDOUT

XFPDIN

XFPCLK

XFPSEL

IRRCV

FRONT PANEL

REM_BUS_P

REM_BUS_N

REM_BUS_N

+5V_DISPLAY

-19V_OUT

-13V5_OUT

-9V_OUT

9190INT*

9190INT*

FSEL1

PROG/INT*

PROG/INT*

DDC_SDA

DDC_SDA

DDC_SCL

DDC_SCL

SDA

SCL

CEC

CEC

P239

RESET*

PV200

PV201

PV202

PV203

PV204

PV205

PV206

PV207

PV208

PV209

PV210

PV211

PV212

PV213

PV214

PV215

PV216

PV217

PV218

PV219

PV220

PV221

PV222

PV223

PV224

PV225

PV226

PV227

PV228

PV229

PV230

PV231

PV232

PV233

PV234

PV235

PV239

PV240

PV241

PV242

PV243

PV244

PV245

PV238

PV237

PV236

NVMDA0

N3

NVMDA1

P4

NVMDA2

P3

NVMDA3

R3

NVMDA4

R4

NVMDA5

P1

NVMDA6

P2

NVMDA7

N4

NVMR/B

N1

NVMCE

L4

NVMRE

M1

NVMWP

N2

NVMWE

M2

NVMALE

L1

NVMCLE

L2

PCLK

U12

RAMCKE

V11

RAMWE

Y14

RAMCAS

W13

RAMRAS

Y13

RAMCS

Y12

RAMDQM

W14

RAMBA1

Y11

RAMBA0

W11

RAMADD0

Y9 RAMADD1

W8 RAMADD2

Y8 RAMADD3

Y7 RAMADD4

W7 RAMADD5

V8 RAMADD6

U8 RAMADD7

V9 RAMADD8

U9 RAMADD9

V10

RAMDAT0

W18

RAMDAT1

Y18

RAMDAT2

W17

RAMDAT3

Y17

RAMDAT4

W16

RAMDAT5

Y16

RAMDAT6

W15

RAMDAT7

Y15

RAMDAT8

V14

RAMDAT9

U14

RAMDAT10

V15

RAMDAT11

V16

RAMDAT12

V17

RAMDAT13

U17

RAMDAT14

V18

RAMDAT15

U18

RAMDAT16

W6

RAMDAT17

Y6

RAMDAT18

W5

RAMDAT19

Y5

RAMDAT20

W4

RAMDAT21

Y4

RAMDAT22

Y3

RAMDAT23

Y2

RAMDAT24

W2

RAMDAT25

W3

RAMDAT26

V4

RAMDAT27

U4

RAMDAT28

V5

RAMDAT29

V6

RAMDAT30

U6

RAMDAT31

V7

RAMADD10

W9 RAMADD11

U10

ATDD0

D2

ATDD1

C2

ATDD2

A1

ATDD3

B2

ATDD4

D3

ATDD5

C3

ATDD6

D4

ATDD7

C4

ATDD8

A4

ATDD9

B4

ATDD10

A3

ATDD11

B3

ATDD12

A2

ATDD13

E4

ATDD14

E3

ATDD15

F4

ATDMARQ

B1

ATIOW

C1

ATIOR

D1

ATIORDY

F3

ATDMACK

E2

ATINTRQ

E1

ATDA0

G3

ATDA1

F1

ATDA2

F2

ATCS0

G1

ATCS1

G2

DAC_A_B/U E17

DAC_B_R/V F17

DAC_C_G/Y F18

DAC_D_CVBS G17

RSET D16

VREF D17

COSYNC K17

VIDP_2 L19

VIDP_3 L20

VIDP_4 L18

VIDP_5 M19

VIDP_6 M20

VIDP_7 M18

VSYNC R17

HSYNC T20

VCLK T19

VCLKx2 K18

AMCLK E19

ALRCLKI E20

ABCLKI F20

ALRCLKO F19

ABCLKO G19

AIN0 C17

AIN1 C16

AOUT0 J17

AOUT1 J19

AOUT2 H20

AOUT3 H19

AOUT4 G20

SPDIF J20

XO

C14

GCLKP

A14

GCLKA

B15

RESET

B14

PLLCFGA J3

PLLCFGP J2

FPCDOUT G4

FPCDIN H4

FPCCLK H3

FPCSTB H1

IRRCV H2

MODRI W19

MODDCD U20

MODDSR V20

MODCTS V19

MODDTR U19

MODRTS Y20

MODRD Y19

MODTD W20

DUPRD T3

DUPTD U3

BOOTSEL0 C10

BOOTSEL1 D10

SPIDATO C13

SPICLK D13

I2CDAT B17

I2CCLK A17

SERADC0 C15

SERADC1 B16

EJTRST K3

EJTDI K4

EJTDO K2

EJTMS K1

EJTCK J1

GPAIO0 B12

V

D

D

P

E

5

V

D

D

P

F5

V

D

D

P

H

5

V

D

D

P

K

16

V

D

D

P

K

5

V

D

D

P

N

5

V

D

D

P

R

5

V

D

D

P

E

7

V

D

D

P

T

7

V

D

D

P

U

7

V

D

D

P

T

9

V

D

D

P

E

10

V

D

D

P

T

11

V

D

D

P

U

11

V

D

D

P

E

12

V

D

D

P

U

13

V

D

D

P

E

15

V

D

D

P

M

16

V

D

D

P

R

16

V

D

D

P

U

16

V

D

D

P

T

15

V

D

D

C

E

13

V

D

D

C

L

17

V

D

D

C

V

12

V

D

D

C

W

10

V

D

D

C

L

5

V

D

D

_D

A

C

A

18

V

D

D

A

A

13

V

D

D

A

D

C

A

16

V

D

D

P-

A

D

12

G

N

D

P

T

5

G

N

D

P

T

6

G

N

D

P

T

8

G

N

D

P

T

10

G

N

D

P

T

12

G

N

D

P

T

13

G

N

D

P

V

13

G

N

D

P

T

14

G

N

D

P

U

15

G

N

D

P

T

16

G

N

D

P

J9

G

N

D

P

K

9

G

N

D

P

L

9

G

N

D

P

M

9

G

N

D

P

L

10

G

N

D

P

K

11

G

N

D

P

K

12

G

N

D

P-

A

2

H

16

G

N

D

P

J1

1

G

N

D

P

J1

2

G

N

D

P

J1

0

G

N

D

P

K

10

G

N

D

C

E

14

G

N

D

C

L

16

G

N

D

C

W

12

G

N

D

C

Y

10

G

N

D

C

M

5

G

N

D

A

A

12

G

N

D

A

D

C

A

15

G

N

D

D

A

C

-P

C

19

G

N

D

D

A

C

-S

B

B

19

G

N

D

D

A

C

-D

B

20

V

D

D

P-

A

2

G

16

DAC_E_Y G18

DAC_F_C H17

VIDP_1 K20

VIDP_0 K19

VIDP_8 M17

VIDP_9 N20

VIDP_10 N19

VIDP_11 N18

VIDP_12 N17

VIDP_13 P20

VIDP_14 P19

VIDP_15 P18

VIDP_19 R18

VIDP_18 R19

VIDP_16 P17

VIDP_17 R20

NVMR/B1

M3

NVMCE1

L3

NVMCD

M4

PNVMCE

Y1

PNVMR/B

W1

SERADC2 D15

PWM C9

BOOTSEL2 D11

HD0

B7

HD1

A7

HD2

B8

HD3

A8

HD4

B9

HD5

A9

HD6

B10

HD7

A10

HA0

B5

HA1

A5

HA2

B6

HA3

A6

HWR

C6

HRD

D6

HCS

D7

HIRQ

C7

HACK

C5

HACK1

D5

HCS1

D8

HIRQ1

C8

PLLSEL D9

SPIDATI B13

TESTMODE D14

GPCIO6 J4

GPCIO7 B18

GPCIO8 C18

GPCIO9 V1

GPCIO10 V2

GPCIO11 U2

GPCIO12 U1

GPCIO13 T1

GPCIO14 T2

GPCIO15 R1

GPCIO16 R2

GPCIO17 B11

GPCIO18 C11

GPCIO19 C12

GPCIO20 V3

V

D

D

P-

A

U

5

V

D

D

C

E

9

V

D

D

_D

A

C

A

19

V

D

D

_D

A

C

A

20

G

N

D

C

E

8

G

N

D

D

A

C

-D

C

20

G

N

D

D

A

C

-D

D

20

G

N

D

A

A

11

G

N

D

P

L

11

G

N

D

P

L

12

G

N

D

P

M

10

G

N

D

P

M

11

G

N

D

P

M

12

IC202

ZR36750

BGA-316

C201

100N

16V

0603

C202

100N

16V

0603

C204

100N

16V

0603

C206

100N

16V

0603

C209

100N

16V

0603

C211

100N

16V

0603

C216

100N

16V

0603

C249

100N

16V

0603

C251

100N

16V

0603

DGND

+3V3D

C203

100N

16V

0603

C264

100N

16V

0603

Near ATAPI conn

+3V3D

DGND

+3V3D

DGND

On bottom of board

+3V3D

DGND

SDRAM decoupling on bottom of board

R200

33R

RAMADD11

1

8

RP216A

100R

2

7

RP216B

100R

6

3

RP216C

100R

5

4

RP216D

100R

1

8

RP217A

100R

2

7

RP217B

100R

6

3

RP217C

100R

5

4

RP217D

100R

1

8

RP218A

100R

2

7

RP218B

100R

6

3

RP218C

100R

5

4

RP218D

100R

1

8

RP219A

100R

2

7

RP219B

100R

6

3

RP219C

100R

5

4

RP219D

100R

1

8

RP220A

100R

2

7

RP220B

100R

6

3

RP220C

100R

5

4

RP220D

100R

1

8

RP213A

56R

2

7

RP213B

56R

6

3

RP213C

56R

5

4

RP213D

56R

R201

100R

R205

100R

HDMI_RESET*

HDMI_RESET*

R202

22R 0603

C255

1N0

50V

0603

C263

1N0

50V

0603

C256

1N0

50V

0603

C257

1N0

50V

0603

C258

1N0

50V

0603

C259

1N0

50V

0603

C260

1N0

50V

0603

C261

1N0

50V

0603

C262

1N0

50V

0603

A0

25

A1

24

A2

23

A3

22

A4

21

A5

20

A6

19

A7

18

A8

8

A9

7

A10

6

A11

5

A12

4

A13

3

A14

2

A15

1

A16

48

G

N

D

46

V

C

C

37

DQ0 29

DQ1 31

DQ2 33

DQ3 35

DQ4 38

DQ5 40

DQ6 42

DQ7 44

DQ8 30

DQ9 32

DQ10 34

DQ11 36

DQ12 39

DQ13 41

DQ14 43

DQ15 45

VPP

13

OE

28 CE

26

V

C

C

Q

47

WE

11 RP

12

G

N

D

27

WP

14

A17

17

A18

16

A19

15

A20

10

A21

9

IC205

TE28F160

L967SW

TSOP-48

NF(32Mb+)

MUTE_RGB

MUTE_RGB

NOTE: Pin B9 is set HIGH to indicate

that this version of hardware

features the HSYNC delay circuit

(see sheet 11)

R203

4K7

0805

R211

4K7

0805

DGND

+3V3D

CONFIGURATION LINKS

P205

DV75

DV79/DV29

6CH*

PG

1.0

04_E129

24-08-04

Production release

PG

1.1

04_E142

23-09-04

Correct BOM error - R320 now fitted