UG-690

EVAL-AD7405FMCZ User Guide

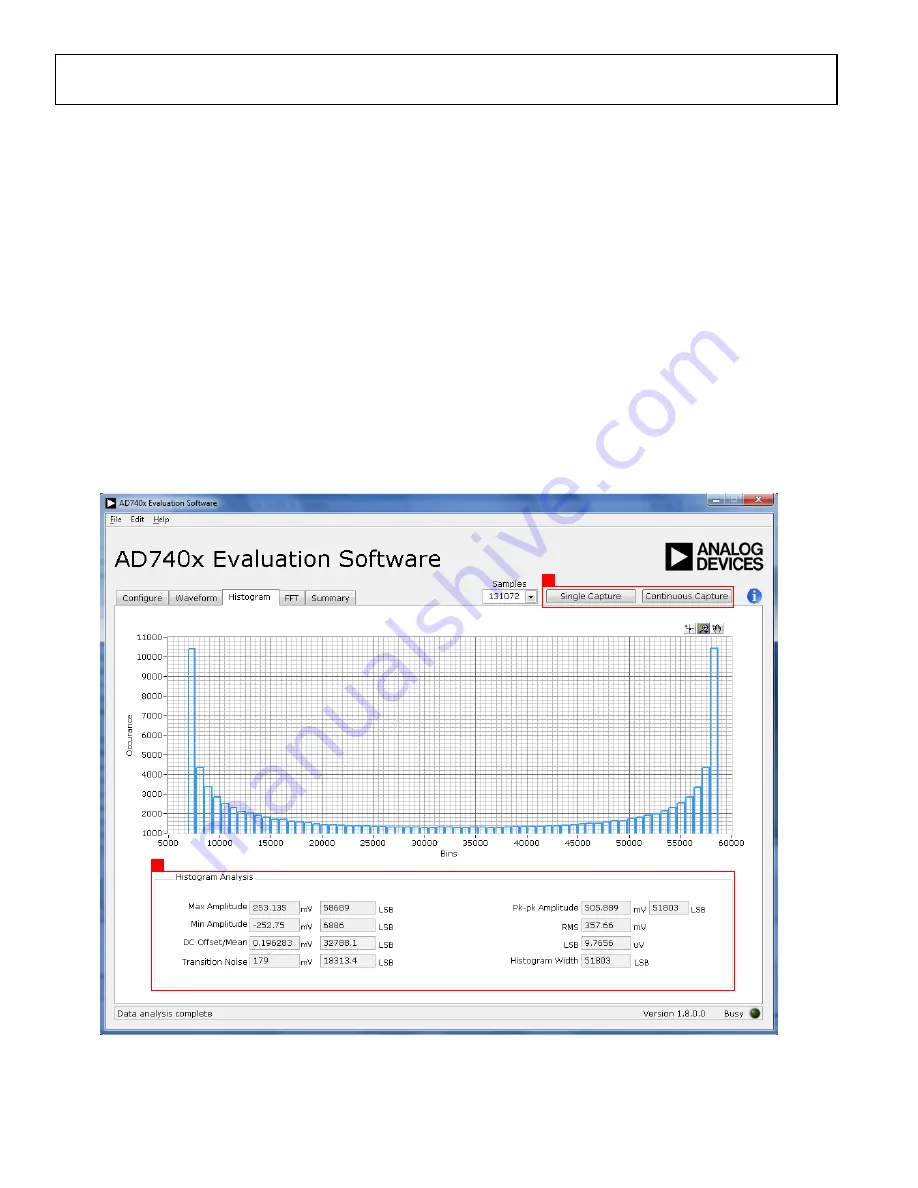

GENERATING A HISTOGRAM

OF THE ADC CODE

DISTRIBUTION

The

Histogram

tab (see Figure 17) can be used to perform ac

testing or, more commonly, dc testing. This tab shows the ADC

code distribution of the input and computes the mean and

standard deviation, which are displayed as

DC Offset/Mean

and

Transition Noise

, respectively, in the

Histogram Analysis

area

(labeled 2 in Figure 17).

AC Input

To perform a histogram test of ac input,

1.

Apply a quality signal source to the VIN+ input on the

board.

2.

Select the

Histogram

tab in the evaluation software main

window

3.

Click the

Single Capture

or

Continuous Capture

button

(labeled 1 in Figure 17).

DC Input

The histogram is more commonly used for dc testing.

To perform a histogram test of dc input,

1.

Select the

Histogram

tab in the evaluation software main

window.

2.

Click

Single Capture

or

Continuous Capture

(labeled 1 in

Figure 17).

Raw data is captured and passed to the PC for statistical

computations, and various measured values are displayed in the

Histogram Analysis

area (labeled 2 in Figure 17).

Figure 17. Histogram Capture Tab

1

2

12304-

017

Rev. 0 | Page 16 of 20