UG-707

ADV8005 Hardware Reference Manual

matrix_prog_en

, Encoder Map,

Address 0xE402[3]

This bit is used to enable the manual mode for the ED/HD colour space converter.

Function

matrix_prog_en

Description

0 (default)

Automatic Mode

1

Manual Mode

Normally, there is no need to enable this feature because the CSC matrix automatically performs the CSC based on the input mode chosen (ED or

HD) and the output color space selected using

. If the user needs to automatically update the CSC coefficients, the following procedure

is followed.

If the user selects the RGB output color space, the ED/HD CSC matrix scaler uses the following equations:

R

=

GY

×

Y

+

RV

×

Pr

G

=

GY

×

Y

− (

GU

×

Pb)

− (

GV

×

Pr)

B

=

GY

×

Y

+

BU

×

Pb

Note:

Subtractions in these equations are implemented in the hardware.

The following registers need to be programmed with these values:

•

gy [9:0] – Reg 0xE405 [7:0], Reg 0xE403 [1:0]

•

gu [9:0] – Reg 0xE406 [7:0], Reg 0xE404 [7:6]

•

gv [9:0] – Reg 0xE407 [7:0], Reg 0xE404 [5:4]

•

bu [9:0] – Reg 0xE408 [7:0], Reg 0xE404 [3:2]

•

rv [9:0] – Reg 0xE409 [7:0], Reg 0xE404 [1:0]

On powerup, the CSC matrix is programmed with the default values shown in

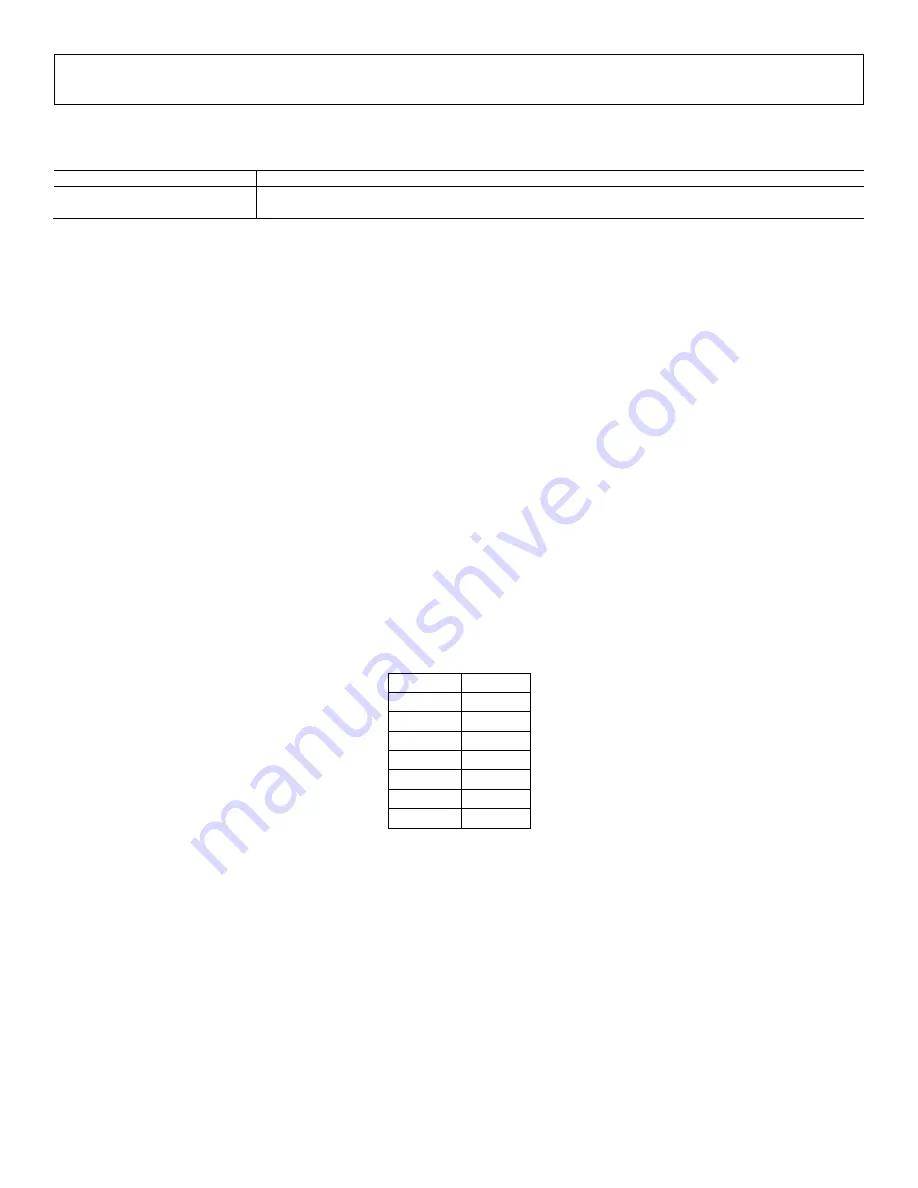

Table 75: ED/HD Manual CSC Matrix Default Values

Register

Default

0x03

0x03

0x04

0xF0

0x05

0x4E

0x06

0x0E

0x07

0x24

0x08

0x92

0x09

0x7C

When the ED/HD manual CSC matrix adjust feature is enabled, the default coefficient values in Reg 0xE403 to Reg 0xE409 are correct for the

HD color space only. The color components are converted according to the following 1080i and 720p standards (SMPTE 274M, SMPTE 296M):

R

=

Y

+ 1.575

Pr

G

=

Y

− 0.468

Pr

− 0.187

Pb

B

=

Y

+ 1.855

Pb

The conversion coefficients should be multiplied by 315 before being written to the ED/HD CSC matrix registers. This is reflected in the default

values for gy = 0x13B, gu = 0x03B, gv = 0x093, bu = 0x248, and rv = 0x1F0.

If the ED/HD manual CSC matrix adjust feature is enabled and another input standard (such as ED) is used, the scale values for gy, gu, gv, bu,

and rv must be adjusted according to this input standard color space. The user should consider that the color component conversion may use

different scale values.

Rev. A | Page 256 of 317