I/O Processor Registers

A-98

ADSP-2126x SHARC Processor Hardware Reference

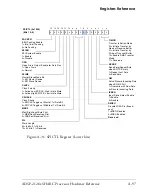

Table A-27. SPICTL Register Bit Descriptions

Bits

Name

Definition

1–0

TIMOD

Transfer Initiation Mode.

Defines the transfer initiation mode

and interrupt generation.

00 = Initiate transfer by read of receive buffer. Interrupt active

when receive buffer is full.

01 = Initiate transfer by write to transmit buffer. Interrupt active

when transmit buffer is empty.

10 = Enable DMA Transfer mode. Interrupt configured by DMA

11 = Reserved

2

SENDZ

Send Zero.

Send Zero or last word when TXSPI is empty.

0 = Send Last Word

1 = Send Zeros

3

GM

Get Data.

When RXSPI is full, get data or discard incoming data.

0 = Discard incoming data

1 = Get more data, overwrites the previous data

4

ISSEN

Input Slave Select Enable.

Enables Slave-Select (

SPIDS

) input for

the master. When not used,

SPIDS

can be disabled, freeing up a

chip pin as a general-purpose I/O pin.

0 = Disable

1 = Enable

5

DMISO

Disable MISO Pin.

Disables MISO as an output in an environ-

ment where the master wishes to transmit to various slaves at one

time (broadcast). Only one slave is allowed to transmit data back

to the master. Except for the slave from whom the master wishes

to receive, all other slaves should have this bit set.

0 = MISO Enabled

1 = MISO Disabled

6

Reserved

8–7

WL

Word Length.

00 = 8 bits, 01 = 16 bits, 10 = 32 bits

9

MSBF

Most Significant Byte First.

1 = MSB sent/received first

0 = LSB sent/received first

10

CPHASE

Clock Phase.

Selects the transfer format.

0 = SPICLK starts toggling at the middle of 1st data bit

1 = SPICLK starts toggling at the start of 1st data bit

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...