UG-207

Evaluation Board User Guide

Rev. A | Page 12 of 16

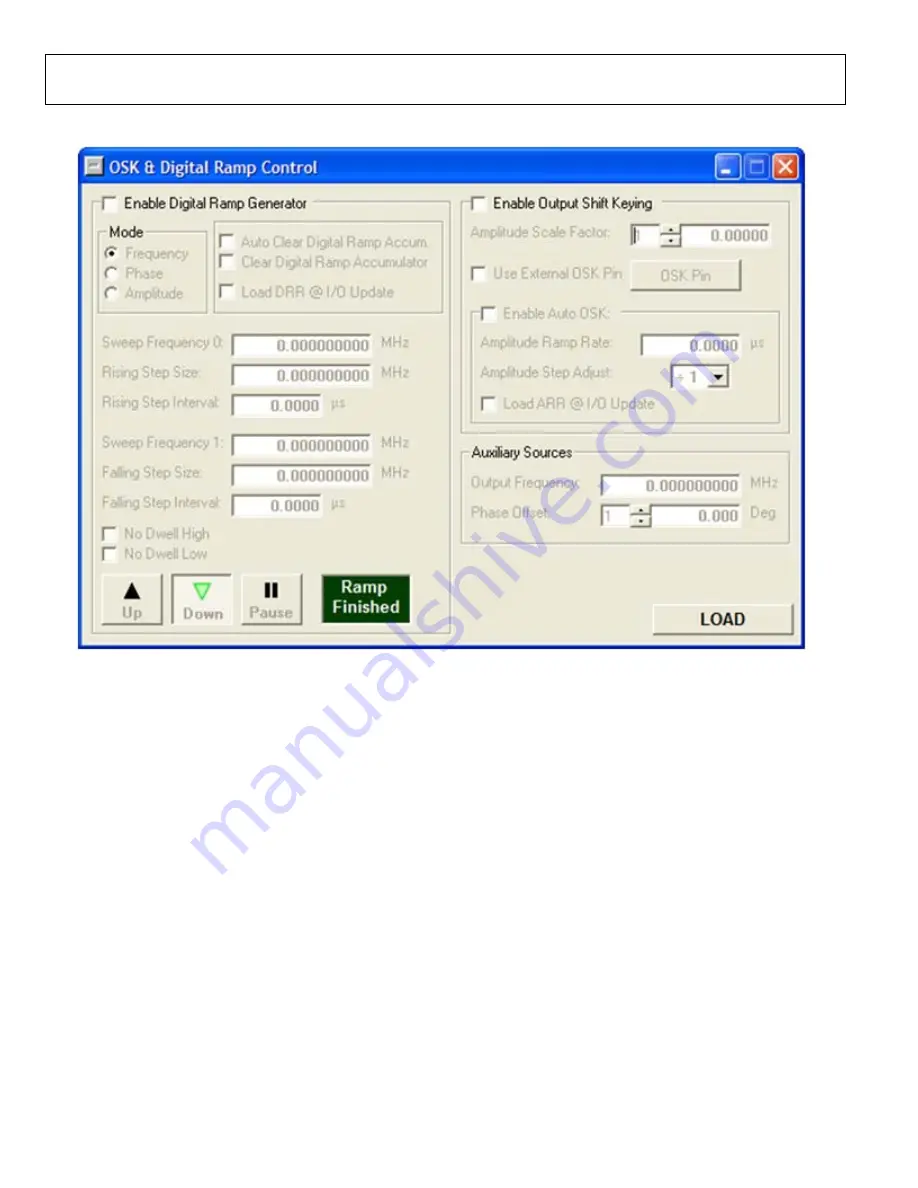

OSK AND DIGITAL RAMP CONTROL

07

48

1-

00

9

Figure 11. OSK and Digital Ramp Control Window

To access the

OSK & Digital Ramp Control

window, select

OSK

Digital Ramp Control Window

from the

View

drop-down menu.

Digital Ramp Generator

To use the digital ramp generator (DRG) function of the AD9910,

select the

Enable Digital Ramp Generator

check box. Under

Mode,

select the frequency, phase, or amplitude to be gener-

ated. The

Auto Clear Digital Ramp Accum

. check box allows

you to set the clear digital ramp accumulator bit when the I/O

update signal is applied or when there is a profile change. The

clear bit is then released.

The

Clear Digital Ramp Accumulator

check box allows you to

set and keep the digital ramp accumulator cleared until that bit

is cleared. The

Load DRR @I/O Update

box allows you to

reload the digital ramp rate when an I/O update is issued or

when there is a profile change.

Sweep Frequency 0

and

Sweep Frequency 1

are the starting

and stopping frequencies of the ramp. Note that this is frequency,

phase, or amplitude depending on which ramp generator is

selected. It is important that the value in the Sweep 0 register

is always less than the value in the Sweep 1

register.

Use the

Rising Step Size

and

Falling Step Size

boxes to set the

step size of the rising or falling ramp. The unit for these changes

depending on what type of ramp is being generated. The

Rising

Step Interval

and

Falling Step Interval

are used to set the time

between each rising or falling step on the ramp. This is in units

of microseconds.

The

No Dwell High

and

No Dwell Low

boxes set the correspond-

ing bit functions in the register map. Use the

Up

,

Down

, and

Pause

buttons at the bottom of the window to control the

direction or to pause the ramp. The

Ramp Finished

message

box lights up when the ramp is complete.