Evaluation Board User Guide

UG-075

Rev. 0 | Page 9 of 16

REGISTER W/R BOX

The

REGISTER W/R

(write/read) box has four buttons and

three check boxes.

The

WRITE

button transfers the values stored in the evaluation

software to the evaluation board. It blinks red when register

values have changed.

The

READ

button transfers the values stored in the evaluation

board to the evaluation software.

The

UPDATE

button issues an I/O update command by writing

0x01 to Register 0x232.

Selecting the

All

check box transfers all of the registers when

the

WRITE

button is clicked. When this check box is cleared,

only the registers whose value has changed are written.

Selecting the

Auto

check box adjacent to the

WRITE

box

forces the evaluation software to write the register changes

to the evaluation board automatically when they occur.

Selecting the

Auto

check box adjacent to the

UPDATE

box

forces the evaluation software to issue an I/O update command

whenever registers are written to the AD951x. It is checked by

default.

SYNC, PD (POWER DOWN), AND RESET BUTTONS

The

SYNC

,

PD

, and

RESET

buttons allow you to control the

SYNC, PD, and RESET pins on the AD951x.

Each button has three options:

Strobe

,

Latch

, and

Release

.

Strobe

activates the pin, and then releases it.

Latch

holds

the pin active until the

Release

command is issued.

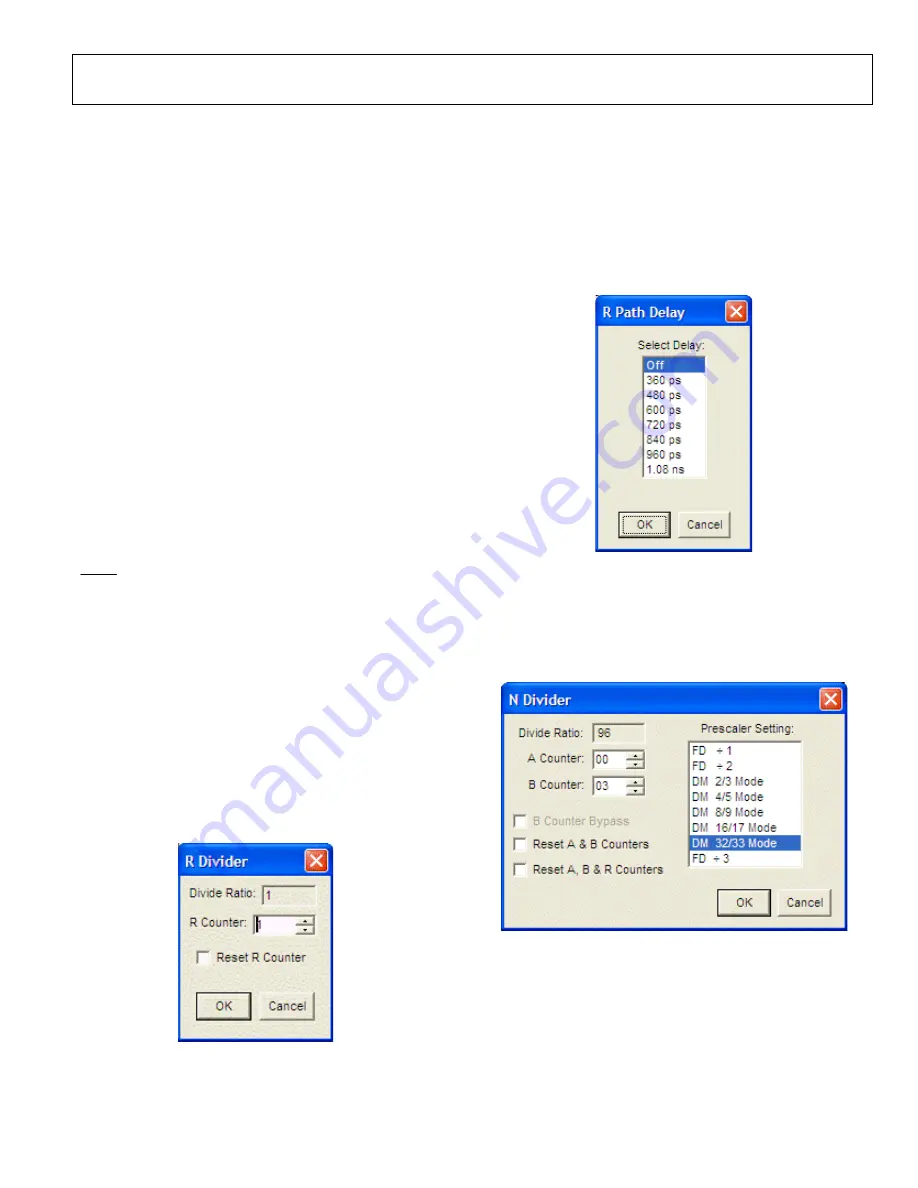

REFERENCE (R) DIVIDER WINDOW

The

R Divider

window shown in Figure 12 is accessed by

clicking the

R DIVIDER

box on the main window. It allows

you to set the reference divider. If this box is colored gray, the

PLL is off. To turn the PLL on, click the

PLL MODE

box at

the top of the main window, and select

Norm Op

.

The

R Divider

window has a check box for holding the

R divider in reset. When the R divider is held in reset, the

PLL loop is opened. Therefore, this feature is seldom used.

087

45-

009

Figure 12. R Divider Window

R AND N DELAY WINDOW

The AD951x features two delay circuits (one on the reference

divider path, and one on the feedback divider path) that allow

the user to control the static phase offset between the reference

input and the PLL output. The

R Path Delay

window shown in

Figure 13 is accessed by clicking the

R DELAY

button on the

main screen. The

R DELAY

box is identical to the

N DELAY

box. These delay settings allow you to vary the static phase

offset of the PLL.

08

74

5-

010

Figure 13. R Path Delay Window

FEEDBACK (N) DIVIDER WINDOW

The reference divider window shown in Figure 14 is accessed by

clicking the

N DIVIDER

box on the main screen. If this box is

colored gray, the PLL is off. To turn the PLL on, click the

PLL

MODE

box at the top of the main screen, and select

Norm Op

.

087

45

-011

Figure 14. N Divider Window

The various modes of the N divider are described in detail in

the AD951x data sheet. For most applications, the 8/9 or 16/17

dual modulus modes are used. For applications requiring a

divider value larger than 131,119, the 32/33 mode is provided.

Different applications require different settings, and you can

experiment with the different settings.

www.BDTIC.com/ADI