SERIES IP400 INDUSTRIAL I/O PACK 40-CHANNEL DIGITAL INPUT MODULE

___________________________________________________________________________________________

-9-

PRELIMINARY SERVICE PROCEDURE

Before beginning repair, be sure that all of the procedures in

Section 2, Preparation For Use, have been followed. Also, refer to

the documentation of your carrier board to verify that it is correctly

configured. Replacement of the module with one that is known to

work correctly is a good technique to isolate a faulty module.

CAUTION: POWER MUST BE TURNED OFF BEFORE

REMOVING OR INSERTING BOARDS

Acromag’s Applications Engineers can provide further technical

assistance if required. When needed, complete repair services are

also available from Acromag.

6.0 SPECIFICATIONS

GENERAL SPECIFICATIONS

Operating Temperature......…..…...0 to +70

°

C.

-40 to +85

°

C (E Version)

Relative Humidity...................….....5-95% Non-Condensing.

Storage Temperature..............…..-25 to +85

°

C.

-55 to +125

°

C (E Version)

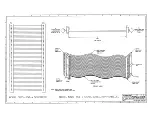

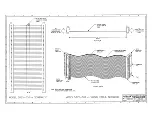

Physical Configuration..................Single Industrial I/O Pack Module.

Length....................................3.880 in. (98.5 mm).

Width.....................................1.780 in. (45.2 mm).

Board Thickness....................0.062 in. (1.59 mm).

Max Component Height..........0.314 in. (7.97 mm).

Connectors:

P1 (IP Logic Interface)...........50-pin female receptacle header

(AMP 173279-3 or equivalent).

P2 (Field I/O)..........................50-pin female receptacle header

(AMP 173279-3 or equivalent).

Power:

+5 Volts (

±

5%)........................15mA Typical; 30mA Maximum.

+12 Volts (

±

5%) from P1.........7.3mA Typical; 8.5mA Maximum.

-12 Volts (

±

5%) from P1..........0mA (Not Used).

Non-Isolated...................................Logic and field I/O common have

a direct electrical connection.

DIGITAL INPUTS

Input Channel Configuration.........40 non-inverting buffered inputs

with a common connection. For

DC voltage applications only,

observe proper polarity. Channels

0-11 can be configured to

generate interrupts.

Input Signal Voltage Range...........0 to +60V DC, Maximum.

Input Signal Threshold..................TTL compatible. 1.5VDC with

200mV of hysteresis, typical.

Thus, Low-to-High threshold is

1.6VDC, High-to-Low is 1.4VDC,

typical. Limited to TTL levels of

0.8VDC (maximum LOW level)

and 2.0VDC (minimum HIGH

level).

Input Resistance...........................100K

Ω

, Typical.

Input Hysteresis............................200mVDC centered at a 1.5VDC

threshold, Typical.

Input Current.................................560uA, Typical at 60V DC.

Interrupt Input Response Time.......250nS minimum to 375nS

maximum, depending on when

the input transition occurs with

respect to the 8MHz clock.

Measured from input transition to

INTREQ0 line assertion.

Resistance to RFI...........................No digital upsets occur for field

strengths up to 10V per meter at

27MHz, 151MHz, & 460MHz per

SAMA PMC 33.1 test

procedures.

Resistance to EMI..........................Unit has been tested with no

digital upsets under the influence

of EMI from switching solenoids,

commutator motors, and drill

motors.

ESD Protection..............................Inputs exhibit no degradation of

performance with repeated ESD

induced voltages to

±

6KV per

DOD-STD-1686.

INDUSTRIAL I/O PACK COMPLIANCE

Specification.................................This module meets or exceeds all

written Industrial I/O Pack

specifications per revision 0.7.1.

Electrical/Mechanical Interface.....Single-Size IP Module.

IP Data Transfer Cycle Types Supported:

Input/Output (IOSel*).............16-bit (D16) word or 8-bit

(D08[EO]) read of data on D0..15.

ID Read (IDSel*)....................32 x 8 ID PROM read on D0..D7.

Access Times (8MHz Clock):

ID PROM Read......................1 wait state (375ns cycle).

Channel Registers Read........1 wait state (375ns cycle).

Interrupt Registers Read........1 wait state (375ns cycle).

Interrupt Registers Write........1 wait state (375ns cycle).

Interrupts:

Handling Format.....................12 interrupt channels are

supported (channels 0-11 only).

An 8-bit vector is provided during

interrupt acknowledge cycles on

D0...D7. The release mechanism

is RORA type (Release On

Register Access).