MC96F6432

June 22, 2018 Ver. 2.9

217

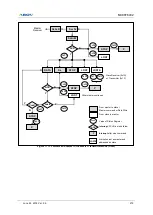

9. This is the final step for master receiver function of I2C, handling STOP interrupt. The STOP bit

indicates that data transfer between master and slave is over. To clear USI0ST2, write

“0” to USI0ST2.

After this, I2C enters idle state.

The processes described above for master receiver operation of I2C can be depicted as the following figure.

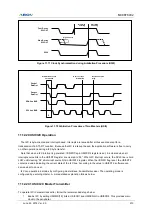

Figure 11.74 Formats and States in the Master Receiver Mode (USI0)

From master to slave /

Master command or Data Write

From slave to master

0xxx

Value of Status Register

ACK

Interrupt

, SCL0 line is held low

Interrupt

after stop command

P

ACK

Arbitration lost as master and

addressed as slave

LOST&

Other master continues

Slave Receiver (0x1D)

or Transmitter (0x1F)

Master

Transmitter

SLA+R

ACK

DATA

Rs

LOST

LOST&

STOP

LOST

S or Sr

SLA+W

Y

N

0x0C

0x85

0x84

0x0C

ACK

STOP

Y

N

0x0D

0x1D

0x45

0x1F

0x44

LOST

P

0x20

P

0x20

Sr

0x44

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...