MC96F6432

June 22, 2018 Ver. 2.9

135

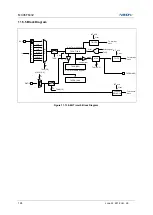

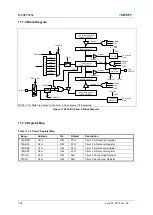

11.6.4 16-Bit PPG Mode

The timer 1 has a PPG (Programmable Pulse Generation) function. In PPG mode, T1O/PWM1O pin outputs

up to 16-bit resolution PWM output. This pin should be configured as a PWM output by setting P1FSRL[5:4] to

‘11’ . The period of the PWM output is determined by the T1ADRH/T1ADRL. And the duty of the PWM output is

determined by the T1BDRH/T1BDRL.

T1MS[1:0]

T1POL

Reload

A Match

T1CC

T1EN

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

fx/4

fx/64

fx/512

fx/2048

fx/8

fx/1

Comparator

16-bit Counter

T1CNTH/T1CNTL

16-bit B Data Register

T1BDRH/T1BDRL

Clear

B Match

Edge

Detector

T1ECE

EC1

Buffer Register B

Comparator

16-bit A Data Register

T1ADRH/T1ADRL

T1IFR

INT_ACK

Clear

To interrupt

block

A Match

Buffer Register A

Reload

Pulse

Generator

T1O/

PWM1O

R

T1EN

3

T1CK[2:0]

2

T1EN

T1CRH

1

ADDRESS:BBH

INITIAL VALUE : 0000_0000B

–

T1MS1

T1MS0

–

–

–

T1CC

–

1

1

–

–

–

X

T1CK2

T1CRL

X

ADDRESS:BAH

INITIAL VALUE : 0000_0000B

T1CK1

T1CK0

T1IFR

–

T1POL

T1ECE T1CNTR

X

X

X

–

X

X

X

A Match

T1CC

T1EN

A Match

T1CC

T1EN

NOTE) The T1EN is automatically cleared to logic

“0” after one pulse is generated at a PPG one-shot mode.

Figure 11.19 16-Bit PPG Mode for Timer 1

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...