6-64

IM 701310-01E

Source Bit Rate, Sample Point, Trigger Level, Hysteresis, and Recessive

Level

Bit Rate

You can select the CAN bus signal transfer rate from the following:

1 Mbps, 500 kbps, 250 kbps, 125 kbps, 83.3 kbps, and 33.3 kbps

If you select the User check box, you can set the transfer rate from 10.0 kbps to 1.000

Mbps in 0.1-kbps steps.

Sample Point

You can set the point for determining the bus level (recessive or dominant) from 18.8 to

90.6% in 3.1% steps.

The DL9000 CAN bus signal trigger circuit samples the input CAN bus signal using the

internal clock and detects the point of change from recessive to dominant. Taking the

detected point of change to be 0% and the point that is bit time after the point of change

to be 100%, you set the sample point in percentage. The bit time is the reciprocal of the

set bit rate.

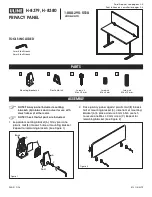

1 bit

1 bit

62.5[%]

18.8[%]

90.6[%]

Sample point

If the sample point is set to 62.5%

Input

waveform

Waveform

sampled using

the internal clock

Trigger Level

You can set the CAN bus signal trigger level for CH1 to CH4 separately.

• The selectable range is 8 divisions within the screen. The resolution is 0.01 divisions.

For example, if the T/div setting is 2 mV/division, the resolution is 0.02 mV.

• You can reset the trigger level to the current offset voltage by pressing RESET.

Hysteresis

See section 6.5 for details.

Recessive Level

Set the recessive level to high (H) or low (L). The logical value of the recessive level is 1

and that of the dominant level is 0 in either setting.

H

The recessive level is higher than the dominant level.

L

The recessive level is less than the dominant level.

6.16 Triggering on a CAN Bus Signal