1-1

1

IM 701830-01E

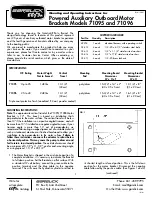

Functions

1.1

Block Diagram

System Configuration

AG

SCSI Interface

Built-in printer

Signal input

Object to be

measured

Video output

External trigger input

GP-IB/RS-232

interface

Screen data

Waveform data

Waveform data

Set-up data

Screen data

Personal Computer

Yokogawa's AG Series

HP-GL compatible

plotter

Printer

Data saved to floppy disk

Trigger out

External SCSI device

DL716

SCSI Interface

Waveform data

Set-up data

Screen data

Waveform data

Centronics compatible

printer

Centronics

interface

External clock input

Block Diagram

ATT

AD

FLT

16

Isolation Block

H

L

+

OFFSET

AMP

+

OFFSET

AMP

ATT

AD

Isolator

FLT

12

Isolation Block

ATT

AD

FLT

12

+

OFFSET

AMP

AD

FLT

Isolation Block

H

L

AMP

RJC

1chip

CPU

ADD

ADD

CPU

SCSI

SCSI

Port

HDD

GPIB

GPIB

Port

RS232

Serial

Port

Centro

Centro

Port

16

8

8

POD-A

POD-B

Bridge Excitation

AD

FLT

16

Isolation Block

Floating Common

+

-

AMP

DIFA

+

-

Strain module

Module Block Diagram

Plug-in module CH1 to Ch8

Acquisition Block Diagram

CPU Block Diagram

High-speed Isolation module

High-speed module

High-resolution, High-voltage, Isolation

/High-resolution, Isolation module

Anti-aliasing filter

Temperature module

Logic Input module

High-speed Logic Probe

Isolated Logic Probe

Acquisition

Data Processing

(ADP)

CH1 to CH4

Acquisition

Data Processing

(ADP)

CH5 to CH8

Optional memory

(Max. 16MW/CH)

Optional memory

(Max. 16MW/CH)

Acquisition

Memory

(200kW/CH)

Acquisition

Memory

(200kW/CH)

Acquisition Control

Logic ASIC

(ACL)

Main Memory

Display ASIC

10.4 Color

TFT Display

Display

RAM

Built-in

printer

FDD

Ext clk in

Ext trig in/out

Acquisition

Data Processing

(ADP)

(Logic1, Logic2)

Acquisition

Memory

Extended Logic

Input

Signal flow

The signal flow at the input end varies depending on the module. Here, the high-Speed

Isolation Module is taken as an example (refer to the block diagram for the signal flow of each

module).

First, the signal input from the input terminal is processed at the input section. In the input

module (High-Speed Isolation), the input signal is attenuated/amplified by the attenuator (ATT),

the adder, and the preamplifier. Then, the signal is isolated through the analog isolator.

Bandwidth limiting is done immediately before the A/D converter.

In the A/D converter, the input signal is sampled at a sampling rate of 10 MS/s (10 million

times in 1 second) and converted to digital data.

The digital signals of the sixteen channels in the CPU board go through the primary and

secondary processing circuits and are finally displayed on the TFT display. In the primary

processing circuit, the ADP(acquisition data processor)/ACL(acquisition control processor)

indicated in the block diagram writes the signal to the memory. In the secondary processing

circuit, the high-speed microprocessor converts the data for data compression and image

processing.

Chapter 1

Functions