34

Tyros2

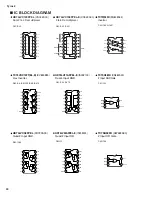

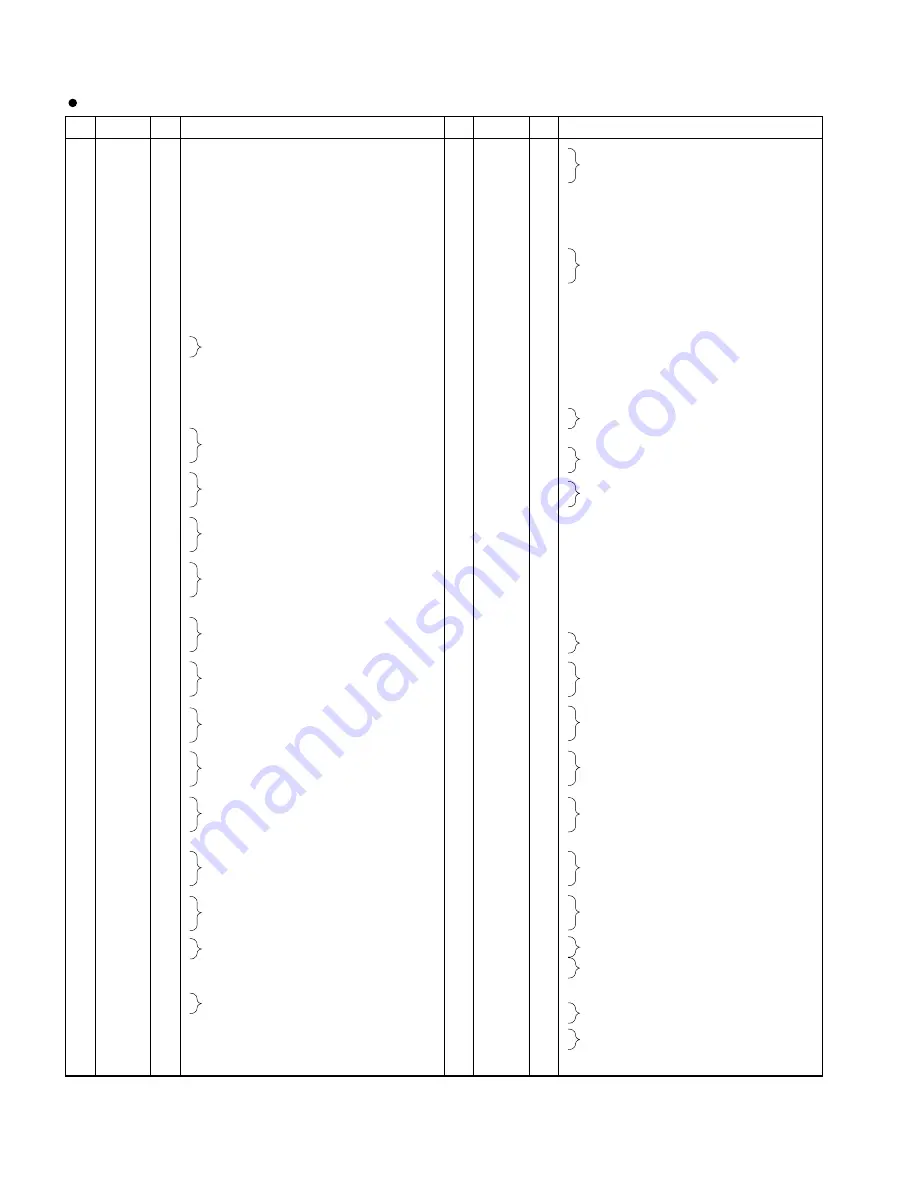

MO

TR

OWNE

BEDIE

MODE

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

LV

DD

XDACK

XDRAK

XDREQ

ATPGEN

Vss

ENCA0

ENCB0

ENCA1

ENCB1

HV

DD

ENCA2

ENCB2

ENCA3

ENCB3

Vss

ENCA4

ENCB4

ENCA5

ENCB5

HV

DD

TSTEN

XIDCS0

XIDCS1

XIDDOE

Vss

HV

DD

XIDWR

XIDRD

XIDMACK

IDMARQ

Vss

IDD0

IDD1

IDD2

IDD3

HV

DD

IDD4

IDD5

IDD6

IDD7

Vss

IDD8

IDD9

IDD10

IDD11

HV

DD

IDD12

IDD13

IDD14

IDD15

Vss

LV

DD

SDRD0

SDRD1

SDRD2

SDRD3

Vss

SDRD4

SDRD5

SDRD6

SDRD7

LV

DD

SDRD8

SDRD9

SDRD10

SDRD11

Vss

SDRD12

SDRD13

SDRD14

SDRD15

LV

DD

SDRA0

SDRA1

SDRA2

SDRA3

Vss

LV

DD

SDRA4

SDRA5

SDRA6

SDRA7

Vss

SDRA8

SDRA9

SDRA10

SDRA11

LV

DD

SDRA12

SDRA13

XSDRWE

XSDRRAS

Vss

XSDRCAS

XSDRCS0

XSDRCS1

SDRDQM

LV

DD

SDRCLK

XTCLR

HV

DD

TESTRAM

Vss

I

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O

O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

I

Power 3.3V

CPU DMA acknowledge

CPU DREQ request acknowledge

CPU DMA request

ATPG test input

Ground

Encoder0 A input

Encoder0 B input

Encoder1 A input

Encoder1 B input

Power 5V

Encoder2 A input

Encoder2 B input

Encoder3 A input

Encoder3 B input

Ground

Encoder4 A input

Encoder4 B input

Encoder5 A input

Encoder5 B input

Power 5V

Test mode change

IDE chip select

IDE bus buffer DIR signal

Ground

Power 5V

IDE write signal

IDE read signal

IDE DMA acknowledge

IDE DMA request

Ground

IDE data bus

Power 5V

IDE data bus

Ground

IDE data bus

Power 5V

IDE data bus

Ground

Power 3.3V

SDRAM data bus

Ground

SDRAM data bus

Power 3.3V

SDRAM data bus

Ground

SDRAM data bus

Power 3.3V

SDRAM address output

Ground

Power 3.3V

SDRAM address output

Ground

SDRAM address output

Power 3.3V

SDRAM address output

SDRAM write signal

SDRAM row address strobe

Ground

SDRAM column address strobe

SDRAM chip select

SDRAM data enable

Power 3.3V

SDRAM clock

Test counter clear

Power 5V

RAM test mode

Ground

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

HV

DD

LEDD0

LEDD1

LEDD2

LEDD3

Vss

LV

DD

XTA22I

Vss

XTA22O

LV

DD

HV

DD

LEDD4

LEDD5

LEDD6

LEDD7

Vss

VCOI

HV

DD

PDOUT

Vss

XRESET

EXTWCI

SDIN

SDOUT

HV

DD

XDSPCS0

XDSPCS2

XDSPCS1

Vss

AUDIOIN0

AUDIOIN1

AUDIOUT0

LV

DD

AUDIOUT1

AUDIOUT2

AUDIOUT3

Vss

AUDIOUT4

AUDIOUT5

AUDIOUT6

LV

DD

HV

DD

CK512

FS256

FS128

Vss

XFS64

ALRCK

XSSYNC

HV

DD

Vss

LV

DD

HV

DD

XDLCS

XLCDCS0

XLCDCS1

Vss

CD0

CD1

CD2

CD3

LV

DD

CD4

CD5

CD6

CD7

Vss

CD8

CD9

CD10

CD11

LV

DD

CD12

CD13

CD14

CD15

Vss

LV

DD

CA1

CA2

CA3

CA4

Vss

CA5

CA6

CA7

CA12

LV

DD

CA13

CA16

XCCS5

XCCS6

Vss

XCRD

XCWR

XCIRQ

XFTMIRQ1

LV

DD

XFTMIRQ2

XFTMIRQ3

FSPLAY

SCANEN

Vss

O

O

O

O

I

O

O

O

O

O

I

O

I

I

I

O

O

O

O

I

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O

I

Power 5V

Port/Test output

Ground

Power 3.3V

XTAL input terminal

Ground

XTAL output terminal

Power 3.3V

Power 5V

Port/Test output

Ground

VCO clock input

Power 5V

PLL phase comparator output

Ground

Reset signal input

External synchronization WC input

Digital sound input

Digital sound output

Power 5V

DSP6 chip select

DSP chip select (reserve)

DSP7 chip select

Ground

Audio data input

Audio data output

Power 3.3V

Audio data output

Ground

Audio data output

Power 3.3V

Power 5V

FS512 clock

FS256 clock

FS128 clock

Ground

FS64 clock (reverse)

System WC (FS)

DSP synchronizing signal output

Power 5V

Ground

Power 3.3V

Power 5V

Data buffer enable

LCD driver chip select

Ground

CPU data bus

Power 3.3V

CPU data bus

Ground

CPU data bus

Power 3.3V

CPU data bus

Ground

Power 3.3V

CPU address input

Ground

CPU address input

Power 3.3V

CPU address input

CPU chip select

Ground

CPU read signal

CPU write signal

CPU interrupt request

Power 3.3V

CPU interrupt request

FS count signal

Scan enable input

Ground

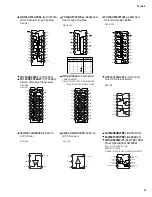

S1L52502F24J000

(X2688A00)

Gate Array

(DGA)

Содержание 2

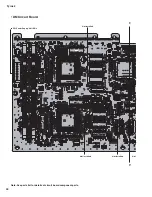

Страница 47: ...47 Tyros2 2NA WE84370 2 2 F F to DAC2A CN101 to LCL CN1 to AJK CN7 Pattern Side ...

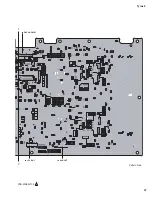

Страница 57: ...57 Tyros2 Note See parts list for details of circuit board component parts P P Pattern Side 2NA WE81690 4 ...

Страница 61: ...61 Tyros2 Note See parts list for details of circuit board component parts R R Pattern Side 2NA WE81690 4 ...

Страница 64: ...64 Tyros2 Note See parts list for details of circuit board component parts PNR Circuit Board T T ...